CUSTOMER_CODE SMUDE DIVISION_CODE SMUDE

advertisement

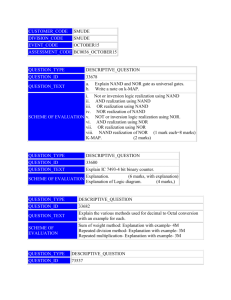

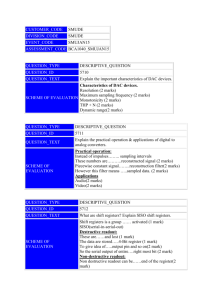

CUSTOMER_CODE SMUDE DIVISION_CODE SMUDE EVENT_CODE OCTOBER15 ASSESSMENT_CODE BC0036_OCTOBER15 QUESTION_TYPE DESCRIPTIVE_QUESTION QUESTION_ID 33677 QUESTION_TEXT a. b. a. b. SCHEME OF EVALUATION State the rules to be followed in BCD addition. Explain Boolean laws. Rules to be followed in BCD addition. Boolean laws:* Communication law * Associative law. * Distributive law. (2.5 marks each, with explanation) QUESTION_TYPE DESCRIPTIVE_QUESTION QUESTION_ID 33678 QUESTION_TEXT a. b. Explain NAND and NOR gate as universal gates. Write a note on k-MAP. i. Not or inversion logic realization using NAND ii. AND realization using NAND iii. OR realization using NAND iv. NOR realization of NAND SCHEME OF EVALUATION v. NOT or inversion logic realization using NOR. vi. AND realization using NOR vii. OR realization using NOR viii. NAND realization of NOR (1 mark each=8 marks) K-MAP. (2 marks) QUESTION_TYPE DESCRIPTIVE_QUESTION QUESTION_ID 33680 QUESTION_TEXT Explain IC 7493-4 bit binary counter. SCHEME OF EVALUATION Explanation. (6 marks, with explanation) Explanation of Logic diagram. (4 marks,) QUESTION_TYPE DESCRIPTIVE_QUESTION QUESTION_ID 73539 QUESTION_TEXT Convert the following numbers to decimal. a. 101.11(2) b. 1101(2) c. 0.111(2) d. 234.32(8) e. 0.427(8) SCHEME OF EVALUATION (Need to solve and get the following answer. Each question has 2M) a. 101.11= 5.75 b. 1101=13 c. 0.111=0.875 d. 234.32=156.15625 e. 0.427=0.544921875 QUESTION_TYPE DESCRIPTIVE_QUESTION QUESTION_ID 73540 QUESTION_TEXT Describe the operations performed by the following arithmetic circuits along with truth table for each. a. Half adder b. Full adder c. Half subtractor d. Full Subtractor SCHEME OF EVALUATION Half adder: (With explanation -1.5M) Addition of two single bits results into single bit Addition of two 1s resulted into two bits. These operations were carried by a logic circuit called half adder which takes two binary digits as input and produces two binary digits on the output terminal known as sum and carry bit. Truth able- 1M Full adder: Accepts three one bit inputs and generates a Sum and a Carry output. (With explanation-1.5M) Truth table: 1M Half subtractor: Subtracts one bit from another. It is used to subtract LSB of the subtrahend from the LSB of the minuend when a binary number is to be subtracted from other. Explanation -1.5M Truth table -1M Half subtractor: Performs subtraction of two bits with borrow generated if any, during previous LSB subtraction. Explanation -1.5M Truth table -1M Explain different types of Slope ADC circuit. (Unit 10, Page 191-193) Ans: (Each with explanation 5M each) Single Slope integrating ADC Dual Slop Integrating ADC QUESTION_TYPE DESCRIPTIVE_QUESTION QUESTION_ID 106596 Prove the following expressions using Boolean rules. What is Demorgan’s Theorem? QUESTION_TEXT a. a+bc=(a+b).(a+c) b. a+a’b=a+b c. a.(b+c)=(a.b)+(a.c) Define the Demorgan’s theorem, which carries 1 Mark. SCHEME OF EVALUATION Prove the above expression using Boolean rules, each carries 3 Marks.