BCA1040A05

advertisement

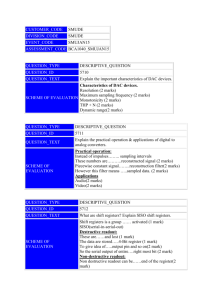

CUSTOMER_CODE SMUDE DIVISION_CODE SMUDE EVENT_CODE OCTOBER15 ASSESSMENT_CODE BCA1040_OCTOBER15 QUESTION_TYPE DESCRIPTIVE_QUESTION QUESTION_ID 5710 QUESTION_TEXT Explain the important characteristics of DAC devices. Characteristics of DAC devices. Resolution (2 marks) Maximum sampling frequency (2 marks) SCHEME OF EVALUATION Monotonicity (2 marks) THP + N (2 marks) Dynamic range(2 marks) QUESTION_TYPE DESCRIPTIVE_QUESTION QUESTION_ID 5712 QUESTION_TEXT What are shift registers? Explain SISO shift registers. Shift registers is a group …… activated (1 mark) SISO(serial-in-serial-out) Destructive readout: These are……and lost (1 mark) The data are stored…..4-Bit register (1 mark) SCHEME OF EVALUATION To give idea of…..output pin and so on(2 mark) So the serial output of entire….right most bit (2 mark) Non-destructive readout: Non destructive readout can be……end of the register(2 mark) However, when the R/W ….lost from the system(1 mark) QUESTION_TYPE DESCRIPTIVE_QUESTION QUESTION_ID 72384 QUESTION_TEXT What are the different types of counters? Explain in detail about Johnson counters. SCHEME OF EVALUATION ● ● ● ● Asynchronous (ripple) counters Synchronous counters Johnson counters Decade counters ● Up-Down counters Johnson Counters: A Johnson counter is constructed using serial-in and serial-out (SISO) shift register. The output of the shift register is connected back to the input after passing it through an inverter. Depending on the initial bit pattern stored in the shift register, the shift register content changes for every clock and the bit pattern gets repeated after 2n clocks, where n is the number of bits in the shift register. These are called “walking ring” counters and have specialist applications like digital-to-analog converters (DAC) etc. QUESTION_TYPE DESCRIPTIVE_QUESTION QUESTION_ID 72386 QUESTION_TEXT Briefly explain adders & subtractors with the help of truth table. SCHEME OF EVALUATION Adders: For single bit adders, there are two general types. A half adder has two inputs, generally labeled A and B, and two outputs, the Sum S and Carry C. S is the two bit XOR of A and B, and C is the AND of A and B. essentially the output of a half adder is the sum of two one-bit numbers, with C being the most significant of these two outputs. (2 marks) A full adder has three inputs: A, B and a carry in C, such that multiple adders can be used to add larger numbers. To remove ambiguity between the input and output carry lines, the carry in is labeled Ci or Cin while the carry output is labeled Co or Cout. (2 marks) Half adder: It is a logical circuit that performs an addition operation on two binary digits. The half adder produces a sum and a carry value which include both binary digits. The drawback of this circuit is that in case of a multibit addition, it cannot include a carry. Logic table for half adder A B C S 0 0 0 0 0 1 0 1 1 0 0 1 1 1 1 0 (1 mark) Full adder: It is a logical circuit that performs an addition operation on three binary digits. The full adder produces a sum and carry value, which are both binary digits. It can be combined with other full adders or work on its own. Input Output A B Ci Co S 0 0 0 0 0 0 0 1 0 1 0 1 0 0 1 0 1 1 1 0 1 0 0 0 1 1 0 1 1 0 1 1 0 1 0 1 1 1 1 1 (2 marks) Full adder can be constructed from two half adders by connecting A and B to the input of one half adder, connecting the sum from that to an input to the second adder, connecting Ci to the other input and the OR the two carry outputs. Equivalently, S could be made the three-bit XOR of A, B and Ci and Co could be made the three-bit majority function of A, B and Ci. The output of the full adder is the two-bit arithmetic sum of three one-bit numbers. (2 marks) Subtractors: A subtractor can be designed using the same approach as that of an adder. The binary operation process is summarized below. As with an adder, in the general case of calculations on multi-bit numbers, three bits are involved in performing the subtraction for each bit: the minuend (Xi), subtrahend (Yi) and a borrow in from the previous (less significant) bit order position (Bi). The outputs are the difference bit (Di) and borrow bit Bi + 1. (3 marks) QUESTION_TYPE DESCRIPTIVE_QUESTION QUESTION_ID 118224 QUESTION_TEXT List out any ten theorems in Boolean Algebra. The important theorems are: Theorem-1: X + X = X Theorem-2: X • X = X SCHEME OF EVALUATION Theorem-3: X + 0 = X Theorem-4: X • 1 = X Theorem-5: X • 0 = 0 Theorem-6: X + 1 = 1 Theorem-7: (X + Y)’ = X’ • Y’ Theorem-8: (X • Y)’ = X’ + Y’ Theorem-9: X + X•Y = X Theorem-10: X •(X + Y) = X Theorem-11: X + X’Y = X+Y Theorem-12: X’ • (X + Y’) = X’Y’ Theorem-13: XY + XY’ = X Theorem-14: (X’+Y’) • (X’ + Y) = Y’ Theorem-15: X + X’ = 1 Theorem-16: X • X’ = 0 QUESTION_TYPE DESCRIPTIVE_QUESTION QUESTION_ID 118227 QUESTION_TEXT Explain the working of multiplexers and de-multiplexers. Multiplexers: In electronics, a multiplexer or mux is a device that performs multiplexing; it selects one of many analog or digital input signals and outputs that into a single line. An electronic multiplexer makes it possible for several signals to share one expensive device or other resources(4 marks) SCHEME OF EVALUATION Digital Multiplexers: In digital circuit design, the selector wires are of digital value. In the case of a 2–to–1 multiplexer, a logic value of 0 would connect I0 to the output while a logic value of 1 would connect I1 to the output. In larger multiplexers, the number of selector pins is equal to 2n where n is the number of inputs. (4 marks) De–multiplexers: In electronics, a demultiplexer is a device taking a single input signal and selecting one of many data–output–lines, which is connected to the single input. A multiplexer is often used with a complementary demultiplexer on the receiving end. A demultiplexer as a single–input, multiple–output switch. (2 marks)