Introduction

advertisement

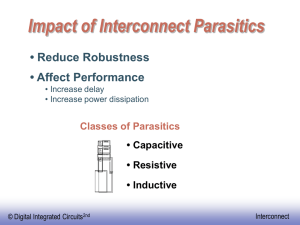

EE5900 Robust VLSI Computer-Aided Design Dr. Shiyan Hu Office: EERC 731 shiyan@mtu.edu Introduction Adapted and modified from Digital Integrated Circuits: A Design Perspective by Jan M. Rabaey, Anantha Chandrakasan, and Borivoje Nikolic. EE141 Integrated © Digital Circuits2nd 1 Introduction Class Time and Office Hour Class Time: MWF 14:05-14:55 (EERC 216) Office Hours: MWF 15:00-15:50 or by appointment, office: EERC 731 Textbook (suggested) Handbook of Algorithms for Physical Design Automation, Charles J. Alpert, Dinesh P. Mehta, Sachin S. Sapatnekar, CRC Press, 2008 Grading: Homework Project Exams EE141 Integrated © Digital 25% 25% 50% Circuits2nd 2 Introduction Course Website http://www.ece.mtu.edu/faculty/shiyan/EE5900Spring11.htm Contact information of instructor Email: shiyan@mtu.edu EERC 731 Instructor’s webpage: http://www.ece.mtu.edu/faculty/shiyan EE141 Integrated © Digital Circuits2nd 3 Introduction Introduction Why is designing digital ICs different today than it was before? What is the challenge? EE141 Integrated © Digital Circuits2nd 4 Introduction The Transistor Revolution First transistor Bell Labs, 1948 EE141 Integrated Circuits2nd © Digital Introduction The First Integrated Circuit First IC Jack Kilby Texas Instruments 1958 EE141 Integrated Circuits2nd © Digital Introduction Intel 4004 Micro-Processor 1971 1000 transistors 1 MHz operation EE141 Integrated © Digital Circuits2nd 7 Introduction Intel 8080 Micro-Processor 1974 4500 transistors EE141 Integrated Circuits2nd © Digital Introduction Intel Pentium (IV) microprocessor 2000 42 million transistors 1.5 GHz EE141 Integrated © Digital Circuits2nd 9 Introduction Not Only Microprocessors Cell Phone Small Signal RF Digital Cellular Market (Phones Shipped) Power RF Power Management 1996 1997 1998 1999 2000 Units 48M 86M 162M 260M 435M Analog Baseband Digital Baseband (DSP + MCU) (data from Texas Instruments) EE141 Integrated © Digital Circuits2nd 10 Introduction Many Chips EE141 Integrated © Digital Circuits2nd 11 Introduction Basic Components In VLSI Circuits Devices Transistors Logic gates and cells Function blocks Interconnects Local interconnects Global interconnects Clock interconnects Power/ground nets EE141 Integrated © Digital Circuits2nd 12 Introduction Cross-Section of A Chip EE141 Integrated © Digital Circuits2nd 13 Introduction CMOS transistors 3 terminals in CMOS transistors: G: Gate D: Drain S: Source nMOS transistor/switch X=1 switch closes (ON) X=0 switch opens (OFF) EE141 Integrated Circuits2nd © Digital pMOS transistor/switch X=1 switch opens (OFF) X=0 switch closes (ON) Introduction An Example: CMOS Inverter +Vd d F= X’ Logic symbol X X F= X’ GR D Transistor-level schematic Operation: X=1 nMOS switch conducts (pMOS is open) and draws from GRD F=0 X=0 pMOS switch conducts (nMOST is open) and draws from +Vdd F=1 EE141 Integrated Circuits2nd © Digital Introduction Moore’s Law In 1965, Gordon Moore noted that the number of transistors on a chip doubled every 18 to 24 months. He made a prediction that semiconductor technology will double its effectiveness every 18 months Not true any more Interconnect delay dominates Variations EE141 Integrated © Digital Circuits2nd 16 Introduction 1959 1960 1961 1962 1963 1964 1965 1966 1967 1968 1969 1970 1971 1972 1973 1974 1975 LOG2 OF THE NUMBER OF COMPONENTS PER INTEGRATED FUNCTION Moore’s Law EE141 Integrated © Digital 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 Electronics, April 19, 1965. Circuits2nd Introduction 17 Transistor Counts 1 Billion Transistors K 1,000,000 100,000 10,000 1,000 i486 i386 80286 100 10 Pentium® III Pentium® II Pentium® Pro Pentium® 8086 Source: Intel 1 1975 1980 1985 1990 1995 2000 2005 2010 Projected EE141 Integrated © Digital Circuits2nd Courtesy, Intel 18 Introduction Moore’s law in Microprocessors Transistors (MT) 1000 2X growth in 1.96 years! 100 10 486 1 P6 Pentium® proc 386 286 0.1 8086 8080 8008 4004 8085 Transistors on Lead Microprocessors double every 2 years 0.01 0.001 1970 EE141 Integrated © Digital Circuits2nd 1980 1990 Year Courtesy, Intel 2000 2010 19 Introduction ITRS Prediction EE141 Integrated © Digital Circuits2nd 20 Introduction Power Dissipation Power (Watts) 100 P6 Pentium ® proc 10 8086 286 1 8008 4004 486 386 8085 8080 0.1 1971 1974 1978 1985 1992 2000 Year Lead Microprocessors power continues to increase EE141 Integrated © Digital Circuits2nd Courtesy, Intel 21 Introduction Power is a major problem 100000 18KW 5KW 1.5KW 500W Power (Watts) 10000 1000 Pentium® proc 100 286 486 8086 10 386 8085 8080 8008 1 4004 0.1 1971 1974 1978 1985 1992 2000 2004 2008 Year Power delivery and dissipation will be prohibitive EE141 Integrated © Digital Circuits2nd Courtesy, Intel 22 Introduction Power density Power Density (W/cm2) 10000 1000 100 Rocket Nozzle Nuclear Reactor 8086 10 4004 Hot Plate P6 8008 8085 Pentium® proc 386 286 486 8080 1 1970 1980 1990 2000 2010 Year Power density too high to keep junctions at low temp EE141 Integrated © Digital Circuits2nd Courtesy, Intel 23 Introduction VLSI Design Cycle System Specification e.g., Verilog Functional Design X=(AB*CD)+(A+D)+(A(B+C)) Y=(A(B+C))+AC+D+A(BC+D)) Logic Design and Synthesis EE141 Integrated © Digital Circuits2nd 24 Introduction VLSI Design Cycle (cont.) Physical Design Fabrication Packaging EE141 Integrated © Digital Circuits2nd 25 Introduction Interconnects Dominate Delay (psec) 300 250 Interconnect delay 200 150 100 Transistor/Gate delay 50 0 0.8 0.5 0.35 0.25 Technology generation (m) Source: Gordon Moore, Chairman Emeritus, Intel Corp. EE141 Integrated © Digital Circuits2nd 26 Introduction New Paradigm for VLSI Design Interconnection Transistors/Cells Conventional Approach Transistors/Cells Interconnection New Approach Interconnect-Driven Design EE141 Integrated © Digital Circuits2nd 27 Introduction Physical Design Given a circuit after logic synthesis, to convert it into a layout (i.e., determine the physical location of each gate and the interconnects between gates). PD EE141 Integrated © Digital Circuits2nd 28 Introduction Nanoscale Challenges Interconnect-limited designs Interconnect performance limitation Interconnect modeling complexity Interconnect reliability (signal integrity) Power barrier High degree of on-chip integration Complexity and productivity System on a chip Variations EE141 Integrated © Digital Circuits2nd 29 Introduction Robust Design For Variations Variations The difference between the designed value and the actual value Robust design Mitigate or compensate for variations Robustness for lithography-induced variations EE141 Integrated © Digital Circuits2nd 30 Introduction Chip Design and Fabrication Lithography Process Designed Chip Layout EE141 Integrated © Digital Circuits2nd Fabricated Chip 31 31 Introduction Photo-Lithography Process optical mask oxidation photoresist removal (ashing) photoresist coating stepper exposure Typical operations in a single photolithographic cycle (from [Fullman]). photoresist development acid etch process step EE141 Integrated © Digital Circuits2nd spin, rinse, dry 32 32 Introduction Lithography System Illumination Mask 193nm wavelength 45nm features Objective Lens Aperture Wafer EE141 Integrated © Digital Circuits2nd 33 33 Introduction Mask v.s. Printing Layout 0.13µ EE141 Integrated © Digital Circuits2nd 0.25µ What you design is NOT what you90-nm get! 0.18µ 65-nm 34 34 Introduction Motivation Chip design cannot be fabricated Gap – Lithography technology: 193nm wavelength – VLSI technology: 45nm features Lithography induced variations – Impact on timing and power Even for 180nm technology, variations up to 20x in leakage power and 30% in frequency were reported. Technology node 130nm 90nm Gate length (nm) Tolerable variation (nm) 90 5.3 53 3.75 35 2.5 28 2 Wavelength (nm) 248 193 193 193 EE141 Integrated © Digital Circuits2nd 65nm 45nm 35 35 Introduction Gap: Lithography Tech. v.s. VLSI Tech. 193nm 28nm, tolerable distortion: 2nm Increasing gap Printability problem (and thus variations) more severe! EE141 Integrated © Digital Circuits2nd 36 36 Introduction Summary Digital integrated circuit design challenges in nanoscale regime High speed Low power Short design time for highly complex circuit having over 1 billion transistors Reliable under variations EE141 Integrated © Digital Circuits2nd 37 Introduction