EE141

advertisement

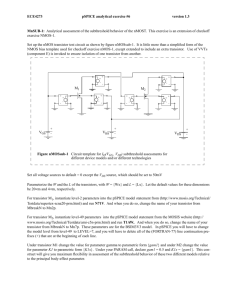

EE141- Spring 2004 Lecture 4 Metrics CMOS Inverter MOS Transistor Model 1 EE141 EE141 Today’s lecture Design Metrics (continued) The CMOS inverter at a glance An MOS transistor model for manual analysis 2 EE141 EE141 1 Important! Labs start next week You must show up in one of the lab sessions If you don’t show up you will be dropped from the class Unless you let me know that you still want to be in the class Homework 2 will be posted later today. Due next Thursday, February 6. 3 EE141 EE141 The Ideal Gate V out Ri = ∞ Ro = 0 Fanout = ∞ NMH = NML = VDD/2 g=∞ V in 4 EE141 EE141 2 An Old-time Inverter 5.0 4.0 NML 3.0 (V ) o u t 2.0 V VM NMH 1.0 0.0 1.0 2.0 3.0 Vin (V) 4.0 5.0 5 EE141 EE141 Example: An Old-time Inverter VOH = 3.6V VOL = 0.4V VIL = 0.6V VIH = 2.3V NMH = VOH – VIH = 1.3V NML = VIL – VOL = 0.2V 6 EE141 EE141 3 Delay Definitions Vin 50% t tpHL Vout tpLH 90% 50% t 10% tf tr 7 EE141 EE141 Ring Oscillator v0 v1 v0 v2 v1 v3 v4 v5 v5 T = 2 × tp × N 8 EE141 EE141 4 A First-Order RC Network R vin vout C tp = ln (2) τ = 0.69 RC Important model – matches delay of an inverter 9 EE141 EE141 Power Dissipation Instantaneous power: p(t) = v(t)i(t) = Vsupplyi(t) Peak power: Ppeak = Vsupplyipeak Average power: Vsupply t +T 1 t +T p(t )dt = Pave = ∫ isupply (t )dt T t T ∫t 10 EE141 EE141 5 Energy and Energy-Delay Power-Delay Product (PDP) = E = Energy per operation = Pav × tp Energy-Delay Product (EDP) = quality metric of gate = E × tp 11 EE141 EE141 A First-Order RC Network R vout vin CL T T E 0→1 = ∫ PDD (t )dt = VDD ∫ i DD (t )dt = VDD 0 T 0 T EC = ∫ PC (t )dt = ∫ v out i L (t )dt = 0 0 VDD ∫ CLdv out 2 = CLVDD 0 VDD ∫ 0 CLv out dv out = 1 2 CLVDD 2 12 EE141 EE141 6 Summary Understanding the design metrics that govern digital design is crucial Cost Robustness Speed Power and energy dissipation 13 EE141 EE141 CMOS Inverter MOS Transistor 14 EE141 EE141 7 What is a Transistor? A MOS Transistor A Switch! |V GS| VGS ≥ VT Ron S D 15 EE141 EE141 NMOS and PMOS NMOS Transistor V GS>0 S PMOS Transistor G G V GS<0 D S D 16 EE141 EE141 8 CMOS Inverter: First Glance N Well VDD VDD PMOS 2λ PMOS In Contacts Out In NMOS Out Metal 1 Polysilicon NMOS GND 17 EE141 EE141 CMOS Inverter First-Order DC Analysis V DD V DD Rp V out V out VOL = 0 VOH = VDD VM = f(Rn, Rp) Rn V in ⫽ V DD V in ⫽ 0 18 EE141 EE141 9 CMOS Inverter: Transient Response VDD VDD tpHL = f(Ron.CL) Rp = 0.69 RonCL Vout Vout CL CL Rn Vin ⫽ 0 Vin ⫽ VDD (a) Low-to-high (b) High-to-low 19 EE141 EE141 CMOS Properties Full rail-to-rail swing Symmetrical VTC Propagation delay function of load capacitance and resistance of transistors No static power dissipation Direct path current during switching 20 EE141 EE141 10 MOS Transistors Types and Symbols D D G G S S NMOS Enhancement NMOS Depletion D D G G B S S NMOS with Bulk Contact PMOS Enhancement 21 EE141 EE141 Threshold Voltage: Concept + VG S S – D G n+ n+ n-channel Depl etion region p-substrate B 22 EE141 EE141 11 The Threshold Voltage Threshold Fermi potential 2φF is approximately - 0.6V for p-type substrates γ – the body factor VT0 is approximately 0.45V for our process 23 EE141 EE141 The Body Effect 0.9 0.85 0.8 0.75 T V (V) 0.7 0.65 0.6 0.55 0.5 0.45 0.4 -2.5 -2 -1.5 -1 V BS -0.5 0 (V) 24 EE141 EE141 12 The Drain Current Charge in the channel is controlled by the gate voltage: Drain current is proportional to charge and velocity: 25 EE141 EE141 The Drain Current Combining velocity and charge: Integrating over the channel: Transconductance: 26 EE141 EE141 13 Transistor in Linear Linear (Resistive) mode VGS S VDS G n+ – V(x) ID D n+ + L x p-substrate B MOS transistor and its bias conditions 27 EE141 EE141 Transistor in Saturation VGS VDS > VGS - VT G D S n+ - VGS - VT + n+ Pinch-off 28 EE141 EE141 14 Saturation For VGD < VT, the drain current saturates k′ W I D = n (VGS − VT )2 2 L Including channel-length modulation k′ W I D = n (VGS − VT )2 (1 + λVDS ) 2 L 29 EE141 EE141 Modes of Operation Cutoff: VGS < VT ID = 0 Resistive: VT < VGS ; VGS − VT > VDS k′ W ⎡ V2 ⎤ ID = n ⎢(VGS − VT )VDS − DS ⎥ 2 L ⎣⎢ 2 ⎥⎦ Saturation: VT < VGS ; VGS − VT < VDS k′ W I D = n (VGS − VT )2 2 L 30 EE141 EE141 15 Current-Voltage Relations A Good Ol’ Transistor 6 x 10 -4 VGS= 2.5 V 5 Resistive Saturation 4 ID (A) VGS= 2.0 V Quadratic Relationship 3 VDS = VGS - VT 2 VGS= 1.5 V 1 0 VGS= 1.0 V 0 0.5 1 1.5 2 2.5 VDS (V) 31 EE141 EE141 A model for manual analysis 32 EE141 EE141 16 Current-Voltage Relations The Deep-Submicron Era x 10 2.5 -4 VGS= 2.5 V Early Saturation 2 VGS= 2.0 V ID (A) 1.5 1 0.5 0 Linear Relationship VGS= 1.5 V VGS= 1.0 V 0 0.5 1 1.5 2 2.5 VDS (V) 33 EE141 EE141 υ n (m/s) Velocity Saturation υsat = 105 Constant velocity Constant mobility (slope = µ) ξc = 1.5 ξ (V/µm) 34 EE141 EE141 17 Velocity Saturation ID Long-channel device VGS = VDD Short-channel device V DSAT VGS - V T VDS 35 EE141 EE141 ID versus VGS -4 6 x 10 -4 x 10 2.5 5 2 4 linear quadratic ID (A) ID (A) 1.5 3 1 2 0.5 1 quadratic 0 0 0.5 1 1.5 VGS(V) Long Channel 2 2.5 0 0 0.5 1 1.5 2 2.5 VGS(V) Short Channel 36 EE141 EE141 18 ID versus VDS -4 6 -4 x 10 VGS= 2.5 V x 10 2.5 VGS= 2.5 V 5 2 Resistive Saturation ID (A) VGS= 2.0 V 3 VDS = VGS - VT 2 VGS= 2.0 V 1.5 ID (A) 4 1 VGS= 1.5 V 0.5 VGS= 1.0 V VGS= 1.5 V 1 VGS= 1.0 V 0 0 0.5 1 1.5 2 VDS(V) Long Channel 2.5 0 0 0.5 1 1.5 2 2.5 VDS(V) Short Channel 37 EE141 EE141 Including Velocity Saturation Approximate velocity: And integrate current again: In deep submicron, there are four regions of operation: (1) cutoff, (2) resistive, (3) saturation and (4) velocity saturation 38 EE141 EE141 19 Regions of Operation Long Channel Short Channel 39 EE141 EE141 An Unified Model for Manual Analysis G S D B 40 EE141 EE141 20 Regions of Operation 2.5 x 10 -4 VDS=VDSAT 2 Velocity Saturated Linear I D (A) 1.5 1 VDSAT=VGT 0.5 VDS=VGT 0 0 Saturated 0.5 1 1.5 2 V DS (V) 2.5 41 EE141 EE141 A PMOS Transistor -4 0 x 10 VGS = -1.0V -0.2 VGS = -1.5V ID (A) -0.4 -0.6 -0.8 -1 -2.5 VGS = -2.0V Assume all variables negative! VGS = -2.5V -2 -1.5 -1 -0.5 0 VDS (V) 42 EE141 EE141 21 Transistor Model for Manual Analysis 43 EE141 EE141 The Transistor as a Switch VGS ≥ VT Ron S ID V GS = VD D D Rmid R0 V DS VDD/2 VDD 44 EE141 EE141 22 The Transistor as a Switch 7 x 10 5 6 4 R eq (Ohm) 5 3 2 1 0 0.5 1 1.5 V DD 2 2.5 (V) 45 EE141 EE141 The Transistor as a Switch 46 EE141 EE141 23 Future Perspectives 25 nm MOS transistor (Folded Channel) 47 EE141 EE141 24