EN=0

advertisement

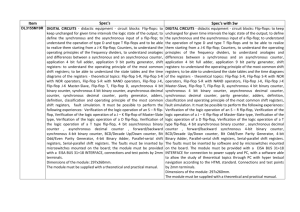

Experiment 8 Counting with Sequential Logic Instructional Objectives: • To use sequential VHDL statements in the design of a T flip-flop – Creating “memory” with VHDL code – Handling feedback of output signals – Using intermediate signals and initialization • To design a T-FF based 4-bit counter using a Structural VHDL design approach • To apply a modular design approach to integrate and test the counter D Flip-flop A D flip-flop changes its current state Q at the rising edge of a clock signal. It’s new state is given by the characteristic equation of the D flip-flop: Q+ = D (Q+ = next state of circuit) entity d_ff_x is port ( D : CLK : Q : end d_ff_x; in std_logic; in std_logic; out std_logic); architecture my_d_ff of d_ff_x is begin dff: process (D, CLK) begin if (rising_edge(CLK)) then Q <= D; end if; end process dff; end my_d_ff; T Flip-flop A T flip-flop toggles its current state Q at the rising edge of a clock signal. It’s new state is given by the characteristic equation of the T flip-flop: Q+ = T XOR Q (Q+ = next state of circuit) Your T flip-flop will include an active high ENable T EN EN CLK T Q+ 0 - - Q (hold) 1 ↑ 0 Q (hold) 1 ↑ 1 not Q (toggle) 4- Synchronous Bit Binary Counter The COUNT Should Increment On Each Rising Edge of The CLK The ENable Should Make the Count Increment (EN=1) Or Hold (EN=0) Output of 4 Flip-Flops Form a 4-Bit Binary COUNT ?? ?? The COUNT Should Increment in A Binary # Sequence 00000001 3-Bit Synchronous Binary Up Counter Output Output Output Output Count Y2 Y1 Y0 0 1 0 0 0 0 0 1 2 3 4 0 0 1 5 6 7 0 1 1 1 0 Toggle Toggle 1 1 0 0 1 1 0 Toggle 0 1 Toggle 0 1 Toggle 0 1 Toggle 0 Y0 “toggles” every count (every clock cycle) Toggle Toggle Y1 “toggles” Toggle every 2 counts Toggle (What conditions precede all Toggle toggles?) Y2 “toggles” every 4 counts (What precedes?) Designing Counter • Set up the sequence of all possible “count” outputs – In standard truth table order • Write the next “count” output value beside each “present output” in the Table • For each Flip-Flop output (Q), ask: – What are the specific PRESENT OUTPUT (Q) and NEXT OUTPUT (Q+) values needed for the desired sequence in each row of the Table? – What input value (T) is needed on the T Flip-Flop producing that output, in order to generate the needed NEXT OUTPUT (Q+) for that row when the proper clock edge occurs?... • Given that the output has its PRESENT value (Q) at the moment – What Boolean Logic combination of the PRESENT OUTPUTS (Q0, Q1, Q2,..) will give you those needed values of “T” ? 4- Synchronous Bit Binary Counter …then determine what Flip-Flop inputs are needed to get the needed output changes… …and design the combinational circuits to generate those inputs (T’s) …from the present outputs You know how you want the Flip-Flop outputs to change… ?? ?? 3-Bit Synchronous Binary Up Counter T0 = ?? Output Output Output Output Count Y2 Y1 Y0 0 1 0 0 0 0 2 3 4 0 0 1 1 1 0 0 1 0 1 0 5 6 7 1 1 1 0 1 1 0 0 0 1 0 1 0 Input Needed Next Output T0 Y0+ 1 1 1 1 1 1 1 1 1 3-Bit Synchronous Binary Up Counter T2 = ?? (K map??) Output Output Output Output Count Y2 Y1 Y0 0 1 2 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 1 0 1 0 1 0 1 0 0 1 1 0 1 0 1 0 3 4 5 6 7 0 Input Needed Next Output T2 Y2+ 0 0 0 1 0 0 0 1 0 Experiment 8 Overview P1: Design and Simulate a T flip-flop P2: Design and Simulate a 4-bit counter – using your T flip-flop module (structural design) – additional gates as needed. – Include a more detailed Block Diagram than the “Black-box Diagram” shown for your lab report Required Counter Schematic Show the Port names for your components Entity Input/Output Port names should match VHDL code Q0 Q1 ?? Label any intermediate signals (matching VHDL) Q2 ?? Show any connections of Inputs/Outputs to LEDs / Switches used for testing (Proc. 3) Experiment 8 Overview P1: Design and Simulate a T flip-flop P2: Design and Simulate a 4-bit counter – using your T flip-flop module (structural design) – additional gates as needed. – Include a more detailed Block Diagram than the “Black-box Diagram” shown for your lab report P3: Integrate 4-bit Counter with your BCD-7seg Display design (unchanged if possible) – – – – Structural Design Visually confirm your counter is working (No ModelSim) Instructor Sign-off Detailed Block Diagram of your Structural Design P4: Verify your Counter with the Logic Analyzer - You may SKIP this…. …but it will cost you 8 points Next Week 1. Finite State Machine Design with VHDL 2. Structural Design Integration of Past Designs into a Digital Alarm System Required Preparations: • VHDL Tutorial on FSM design • Read Lab Instructions • Prepare a “State Transition Diagram” and “Present State / Next State (PS/NS) Table” for your Alarm System Finite State Machine – Turned in at BEGINNING of Next Week’s Lab • Prepare a draft of the Structural Design for the complete Alarm System (assuming a module exists for the Alarm FSM). – Turned in at BEGINNING of Next Week’s Lab