Chapter 6 Registers and Counters

advertisement

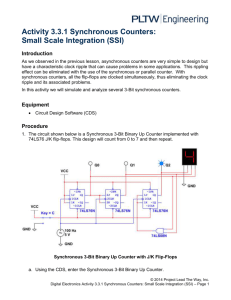

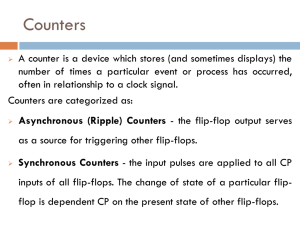

Registers and Counters Chapter 6 Registers and Counters • A register is a group of flip-flops • Each flip-flop stores one bit of info • A counter is a register that goes through a predetermined sequence of binary states Registers 4-bit register with • D Flip-flops • Common clock input • Common clear input; when Clear=0 flip-flops reset asynchronous Register with parallel load Exercise: Explain how this register works. Why is it necessary to feed 𝐴𝑛 back to the combinational input circuit? What if this was not done? Shift Registers What happens with every clock pulse? Serial transfer Serial addition Exercise: Describe how you add two binary numbers by hand. How do you apply this to design a serial adder? Assume you have two n-bit shift registers. Design a circuit that adds one bit at a time and stores the result in one of the shift registers. How do you handle the carries? Hint: you may need one additional flip-flop. Indicate the clock connections of the shift registers and the flip-flop. Serial adder Serial adder Serial adder 𝐽𝑄 = 𝑥𝑦 𝐾𝑄 = 𝑥 ′ 𝑦 ′ = (𝑥 + 𝑦)′ 𝑆 = 𝑥⨁𝑦 ⊕ 𝑄 Exercise: Explain how this circuit works. Obtain the excitation/input equations for the JK Flip-flop and the equation for the sum 𝑆. Run an example sum assuming the circuit uses two 3-bit shift registers. Universal shift register 1. Clear control to clear register to 0 2. Clock input to synchronize operations 3. Shift-right control to enable operation and associated input and output lines 4. Shift-left control to enable operation and associated input and output lines 5. Parallel-load control to enable parallel transfer and the n input lines 6. n parallel output lines 7. Control state to leave information in the register unchanged Universal shift register Exercise: explain how this universal shift register works Universal shift register Universal shift register Counters • A counter is a register that goes through a prescribed sequence of states upon the application of input pulses • Two types of counters – Ripple counters – Synchronous counters Ripple Counters 4-bit ripple binary counter with T Flip-flops Exercise: Obtain the state table. Ripple counters 4-bit binary ripple counter with D flip-flops Exercise: Explain how this counter works. Ripple Counters BCD ripple counter State diagram of a decimal BCD counterr BCD ripple counter Exercise: Obtain the excitation equation and the state table. Explain how this counter works. Three-decade decimal BCD counter Synchronous Counters • Simple design procedure • Least significant digit Flip-flop is complemented with every clock pulse • A flip-flop in any other position is complemented when all the bits in the lower significant positions are equal to 1 Synchronous Counters Exercise: Using the excitation tables for the JK flip-flops explain how this counter works. Up-down binary counter Countdown binary counter: • Least significant bit is complemented with each clock pulse • A bit in any other position is complemented is all lower significant bits are all equal to 0 BCD counter Flip-flop input equations are simplified using maps 𝑇𝑄1 = 1 𝑇𝑄2 = 𝑄′8 𝑄1 𝑇𝑄4 = 𝑄2 𝑄1 𝑇𝑄8 = 𝑄8 𝑄1 + 𝑄4 𝑄2 𝑄1 𝑦 = 𝑄8 𝑄1 Binary counter with parallel load Exercise: Explain how this counter works: • When Load is high/low; • When Clear is high/low; • When Count is high/low; • How should Load and Clear be for counting? Binary counter with parallel load BCD counter implemented with counter with parallel load Other Counters Counter with unused states Other Counters Counter with unused states Ring counter Johnson counter Connecting complemented LSB to ring counter input doubles the number of states of ring counter. What happens if counter starts from an unused state? Homework Assignment • • • • • • • 6.4 6.6 6.9 (a) 6.18 6.21 6.23 6.26

![Lesson 8_3–Synchronous Counters[1]](http://s2.studylib.net/store/data/005727557_1-25e5d6e99f500ad17373ec48380a1b3c-300x300.png)