implement a full adder using FPGA

advertisement

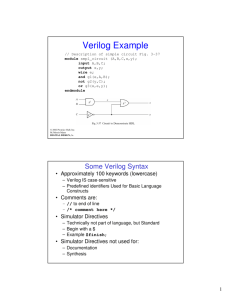

Verilog Section 3.10 Section 4.5 Keywords • Keywords are predefined lowercase identifiers that define the language constructs – Key example of keywords: module, endmodule, input, output, and wire. assign • The assignment is said to be sensitive to the variables in the RHS expression because anytime a variable in the RHS changes during the simulation, the RHS expression is reevaluated and the result is used to update the LHS. Semicolon • Each statement must end with a semicolon (;) Bitwise Logic Operation • Bitwise means 1 bit at a time Bitwise logic operator Verilog AND a&b OR a|b XOR a^b INVERT ~a NAND ~(a&b) NOR ~(a|b) XNOR !(a^b) wire You can think of a wire as a wire in a circuit where actual voltages Could be measured. Wire example Use & for AND operation Use tilda (~) for the INVERT operation Use | for the OR operation Waveform Using Verilog Primitives • Verilog also has keywords such as and or and not. The output of a primitive must be listed first. Gate Delays • In Verilog, the propagation delay of a gate is specified in terms of time units and is specified by the symbol #. • `timescale 1ns/100ps – The first number specifies the unit of measurement for time delays. – The second number specifies the precisions for which the delays are rounded off. Gate Delay E is not defined until after 1 ns. Gate Delay E is not defined until 1 ns. W is not defined until 2 ns. This means that D is not defined until 3 ns. Binary Addition Example Derivation of ∑ (ES112 Slides) B A ∑ 0 0 0 1 0 1 0 1 1 1 1 0 Question: What primitive best implements ∑? • Inputs: A, B • Outputs: ∑=𝐴𝐵 + 𝐴𝐵 = 𝐴 ⊕ 𝐵 Derivation of Carry Out (ES112 Slides) B A Co 0 0 0 1 0 0 0 1 0 1 1 1 Question: What primitive best implements Co? • Inputs: A, B • Outputs: Co =A∙B Implementation of a Half-Adder Limitation of a Half Adder A half-adder does not account for carry-in. Truth Table for a Full Adder carry-in Karnaugh Map For the Sum Bit (ES112 Review) 𝑆 = 𝑥 ′ 𝑦 ′ 𝑧 + 𝑥 ′ 𝑦𝑧 ′ + 𝑥𝑦 ′ 𝑧 ′ + 𝑥𝑦𝑧 =𝑧 ′ 𝑥 ′ 𝑦 + 𝑥𝑦 ′ + 𝑧 𝑥 ′ 𝑦 ′ + 𝑥𝑦 =𝑧 ′ 𝑥 ′ 𝑦 + 𝑥𝑦 ′ + 𝑧 𝑥 ′ 𝑦 + 𝑥𝑦 ′ ′ =𝑧 ⊕ (𝑥 ⊕ 𝑦) Karnaugh Map For the Carry-Out Bit (ES112 Review) C = 𝑥 ′ 𝑦𝑧 + 𝑥𝑦 ′ 𝑧 + 𝑥𝑦 = 𝑧 𝑥 ⊕ 𝑦 + 𝑥𝑦 Implementation of a Full Adder (carry-in) C = 𝑧 ⊕ (𝑥 ⊕ 𝑦) 𝑆 = 𝑧 𝑥 ⊕ 𝑦 + 𝑥𝑦 Schematic of a Full Adder Half-adder Half-adder(not including the bubble) Build a Verilog Representation of a Full Adder Circuit Build a half adder circuit Build a test bench for the adder circuit Assemble a full adder circuit Build a test bench circuit to test the full –adder • Write the code to implement the adder circuit on FPGA • • • • Build a Half-Adder Circuit (Figure 4.5) Build a Test Bench in Verilog Ideas: (page 112 of the textbook) 1. reg 2. Initial statement 3. Assign value to a single bit 4. $finish 1’b0=one binary digit with a value of 0 1’b1=one binary digit with a value of 1 Initial, $finish • inital: keyword used with a set of statements that begin executing when simulation is initialized. • $finish: specifies the termination of simulation. Block statement A block statement consists of several statements that are executed in sequence from top to bottom. Build a Full-Adder Circuit M1 M2 w1 w2 w3 Full-Adder Top Level Circuit Build a FPGA Top Level Circuit (x) (y) (z) (s) (c) See gates2.pdf (available from the course website) for reference