lab3

advertisement

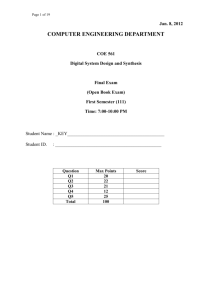

CMPEN270 – Digital Design Practice Lab3 – Implementation of a Combinational Logic Circuit in VHDL Penn State Erie, The Behrend College 1 Discussion The objective of this lab is to design, simulate, and implement a simple combinational logic circuit from its description in the form of a word statement into a working circuit. The circuit will determines the binary sum of three bits of input. This will be accomplished using Xilinx 14.7 ISE and ISIM. Finally the circuit will be synthesized, turned into a form that can be used to program the XC9500 IC on the the Programmable Logic Device Trainer board, PLDT-3, by R.S.R Electronics Company. 2 Pre-Lab The PLDT-3 board features a Complex Programmable Logic Device (CPLD), XC95108, which is made by Xilinx Corporation. An understanding of how the components on the PLDT-3 board are connected to the pins of the Xilinx CPLD is required in order to implement practical design. Open the PLDT-3 Trainer Manual, posted on the class web site, to pages 8 and 9 to complete Table 1 on green engineering paper. SWITCH CPLD PIN RED LEDs S6-1 LED-9 S6-2 LED-10 S6-3 LED-11 S6-4 LED-12 S7-1 LED-13 S7-2 LED-14 S7-3 LED-15 S7-4 LED-16 CPLD PIN Table 1: The connections of devices on the PLDT-3 board to the Xilinx CPLD. A full adder is described by the following word statement. Design a circuit called Full Adder. The circuit takes as input three bits called a, b, and c and adds them together in binary. For example if a=1, b=1, and c=0, the sum would 1+1+0=2. However, the result must be represented in binary so the output would be 10. The two bits of output from the full adder circuit are called sum1 and sum0, where sum1 is the most significant bit. Create a truth table showing the correct values of the output signals for each combination of the inputs. Use a as MSB and c as LSB. Write a SOPmin equation for each of the output signals. Draw a schematic diagram for both bits of output using the schematic guidelines posted on the class web page. Write the VHDL code for the full adder using the shell given on ANGLE. Edit the code in Notepad, save a copy, and turn-in a hard copy. 1 3 In-lab Task A 1. Create a new Xilinx ISE project for this lab using the instruction provided in lab1 with one exception. a. Make sure to select “HDL” as the Top-level source type: in the New Project Wizard pop-up. b. Copy the full adder VHDL file created in the prelab into the project directory. c. Add the full adder to the project by selecting Project → Add Source. d. In the Adding Source Files… pop-up, make sure to select “All” for the Association. Figure 1: Adding the lab3.vhd VHDL module to a project. e. Make sure that the Simulation radio button is selected at the top of the Design window. f. Down load the self checking testbench file from Angel and add them to the project. g. Use ISIM to verify that the circuit works correctly for the entire truth table. The timing diagram in Figure 2 has had its unnecessary signals removes and zoomed out. 2 Figure 2: A successful self-checking simulation run of the full adder. 2. Download the synthesized full adder to the XC95108 chip on the PLDT-3 board and test the circuit. a. Make sure that the Implementation radio button is selected at the top of the Design window. b. Create a new source module Project → New Source. c. In the New Source wizard pop-up select Implementation Constrain File as the Source Type, and lab3 as the File name. d. Click Next, then Finish. e. In order to implement the full adder on the Xilinx chip, the signals in the entity description must be bound to pins of the chip. The PLDT-3 board has red LEDs and toggle switches S6 and S7, located on the bottom of the board. The signals a, b and c will be assigned to toggle switches S6-1, S6-2 and S6-3 attached to CPLD pins 11, 7 and 6 respectively. The outputs sum1 and sum0 will be displayed on the two rightmost red LEDs numbered 9 and 10 which are connected to CPLD pins 35 and 36 respectively. Listing 1 gives the code to put in the lab3.ucf file to make the correct associations between the signals in the port description and the pins of the CPLD. NET NET NET NET NET "A" "B" "C" "SUM1" "SUM0" LOC LOC LOC LOC LOC = = = = = "P11"; "P7"; "P6"; "P35"; "P36"; Listing 1: The ICF file for the full adder. f. The full adder will be synthesize. Select fa.vhd in the Hierarchy pane of the Design window. Double-click on Implememt Design in the Processes pane. It will go through synthesis and design implementation automatically before the programming file is generated. Expand the items in the Processes pane by clicking the plus signs (+) next to them. A green checkmark next to all the processes indicates that the process was run successfully. A yellow exclama- 3 tion mark represents a warning for the process that was run. A red X-mark means that there are errors in the design. The error descriptions can be found in the bottom pane of the window. g. Plug the AC adaptor into an outlet, and connect it to the PLDT3 target board. Connect the PC to the target board with the parallel cable. h. Double-click on Manage Configuration Project (located under Configure Target Device). This will start the program called iMPACT. i. The Impact program will open. Select create a new project, in the Automatically create and save a project pop-up click Yes, and then select Configure devices using Boundary Scan (JTAG). Use the drop down menu to select Automatically connect to a cable and identify boundary scan chain and then click OK. j. Right click to add device and navigate to the lab3 project folder. Select lab3.jed. Click Open. k. Right-click on the Xilinx chip box in the iMPACT window. Use the pull-down to choose Program. In the Program Options window, make sure that only Erase Before Programming is checked. Click OK. The processing time should take about 5 to 15 second depending on the speed of the PC and the complexity of the circuit. The programming process ends with the message “Programming Succeeded” in the message window. l. Check if that the circuit is working properly by using the toggle switches S6-1, S6-2 and S6-3 to generate values for a, b, and c. The LEDs should turn on and off according the values given by the truth table. 4