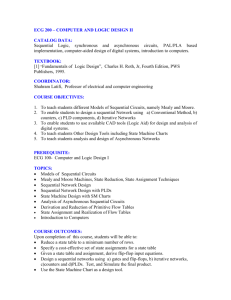

Lecture-9-10: Sequential Coding - Dr. Imtiaz Hussain

advertisement

Advanced FPGA Based System Design Lecture-9 & 10 VHDL Sequential Code By: Dr Imtiaz Hussain imtiaz.hussain@faculty.muet.edu.pk 1 Contents • Introduction • Process • Signals & Variables • IF 2 Introduction • VHDL Code is Inherently Concurrent. • PROCESSES, FUNCTIONS, and PROCEDURES are the only sections of code that are executed sequentially. • One important aspect of sequential code is that it is not limited to sequential logic. • With it we can build sequential circuits as well as combinational circuits. • Sequential code is also called behavioral code. 3 Introduction • The statements discussed in this lecture are all sequential, that is, allowed only inside ROCESSES, FUNCTIONS, or PROCEDURES. • They are: IF, WAIT, CASE, and LOOP. 4 Process • The statements discussed in this lecture are all sequential, that is, allowed only inside ROCESSES, FUNCTIONS, or PROCEDURES. • They are: IF, WAIT, CASE, and LOOP. • A PROCESS is a sequential section of VHDL code. • It is characterized by the presence of IF, WAIT, CASE, or LOOP, and by a sensitivity list (except when WAIT is used). • A PROCESS must be installed in the main code, and is executed every time a signal in the sensitivity list changes (or the condition related to WAIT is fulfilled). 5 Process • Its syntax is shown below. 6 Process Example • DFF with Asynchronous Reset 7 8 Signals and Variables • VHDL has two ways of passing non-static values around: by means of a SIGNAL or by means of a VARIABLE. • A SIGNAL can be declared in a PACKAGE, ENTITY or ARCHITECTURE (in its declarative part). • While a VARIABLE can only be declared inside a piece of sequential code (in a PROCESS, for example). • Therefore the value of the SIGNAL can be global, the VARIABLE is always local. 9 Signals and Variables • The value of a VARIABLE can never be passed out of the PROCESS directly. • If necessary, then it must be assigned to a SIGNAL. • On the other hand, the update of a VARIABLE is immediate, that is, we can promptly count on its new value in the next line of code. • That is not the case with a SIGNAL (when used in a PROCESS), for its new value is generally only guaranteed to be available after the conclusion of the present run of the PROCESS. 10 Signals and Variables • The assignment operator for a SIGNAL is ‘‘<=’’ (ex: sig <= 5). • And for a VARIABLE it is ‘‘:=’’ (ex: var := 5). 11 IF • As mentioned earlier, IF, WAIT, CASE, and LOOP are the statements intended for sequential code. • Therefore, they can only be used inside a PROCESS, FUNCTION, or PROCEDURE. • The natural tendency is for people to use IF more than any other statement. • The syntax of IF is shown below. 12 IF (Example) 13 Example: One Digit Counter • 1-digit decimal counter (0 to 9 to 0). • It contains a single-bit input (clk) and a 4-bit output (digit). • A variable, temp, was employed to create the four flip-flops necessary to store the 4-bit output signal. 14 15 Example: One Digit Counter with Asynchronous Reset I/P clk C O U N T E R digit(3:0) rst 16 Example: Shift Register • Figure shows a 4-bit shift register. • The output bit (q) must be four positive clock edges behind the input bit (d). • It also contains an asynchronous reset, which must force all flip-flop outputs to ‘0’ when asserted. 17 Example: Shift Register 18 Example: Shift Register 19 WAIT • Wait Statement has three different formats. 20 WAIT UNTIL • The WAIT UNTIL statement accepts only one signal, thus being more appropriate for synchronous code than asynchronous. • Since the PROCESS has no sensitivity list in this case, WAIT UNTIL must be the first statement in the PROCESS. • The PROCESS will be executed every time the condition is met. 21 WAIT UNTIL Example 22 WAIT ON • WAIT ON, on the other hand, accepts multiple signals. • The PROCESS is put on hold until any of the signals listed changes. • In the example below, the PROCESS will continue execution whenever a change in rst or clk occurs. 23 WAIT ON • In the example below, the PROCESS will continue execution whenever a change in rst or clk occurs. 24 WAIT FOR • Finally, WAIT FOR is intended for simulation only (waveform generation for test benches). • Example: WAIT FOR 5ns;. 25 Example: DFF • DFF with Asynchronous Reset using WAIT ON instead of IF. 26 27 Example: One Digit Counter • Use WAIT UNTIL to design a one digit counter clk C O U N T E R digit(3:0) rst 28 29 To download this lecture visit imtiazhussainkalwar.weebly.com END OF LECTURE-9-10 30