Intro to Verilog

advertisement

GWU – ECE 2140

Spring 2012

Revised by Scott Trocchia

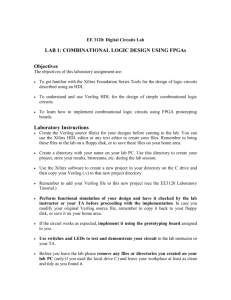

What are FPGAs? What’s inside them?

Brief Verilog History

What is Verilog?

Levels of Verilog Coding

Modules

Lots of Operators

Verilog Modeling

◦ Always blocks

◦ Continuous assignments

FPGA =

Field-Programmable Gate Array

◦ Include space for lots of logic gates

◦ Can be programmed…

…and reprogrammed ~100,000 times

◦ Benefits include:

Cheap

Easy to program (barring errors)

Short amount of time for commercialization

etc.

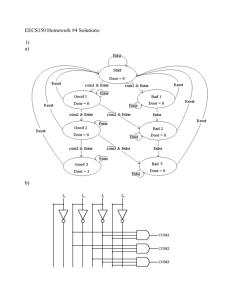

A: This

Let’s go back to 1984…

A world without Verilog…

◦ … was boring

In 1984, the language was created by

Gateway Design Automation, Inc.

Hardware Description Language

◦ Not meant to be understood for your operating

system (Windows, Mac, Linux)

Used to describe digital systems, such as

◦ Register (memory)

◦ CPU

◦ Network switch

Built-in functions: not, and, nand, nor, or,

xor, xnor, buf, …

Behavioral level

◦ A functional representation

◦ How does my circuit work?

Register-Transfer Level (RTL)

◦ How is data transferred from inputs to outputs?

Gate Level

◦ What gates are contained within my circuit?

module half_adder(x, y, sum, carry);

module half_adder(A, B, Sum, C_out);

input x;

input y;

output sum;

output carry;

input A;

input B;

output Sum;

output C_out;

assign sum = x ^ y;

assign carry = x & y;

xor(Sum, A, B);

and(C_out, A, B);

endmodule

endmodule

module Multiplexer(In, Select, Out);

input [3:0] In;

input [1:0] Select;

output reg Out;

always @ (*) begin

case (Select)

2'b00: Out <=

2'b01: Out <=

2'b10: Out <=

2'b11: Out <=

endcase

end

endmodule

In[0];

In[1];

In[2];

In[3];

Verilog is case-sensitive,

so be mindful!

reg – register – stores a value

wire – used for connecting logic

Number representation

◦ Typical format is:

(#bits)’(RADIX)(number)

RADIX: b=binary, h=hex, d=decimal

◦ Example: 4’b1110 = 4’hE = 4’d14

◦ Negative numbers in 2’s complement

•

•

•

•

•

•

•

•

Arithmetic

Logical

Relational

Equality

Reduction

Shift

Concatenation

Conditional

Symbol Arithmetic

operation

*

Multiply

/

Divide

+

Add

Subtract

%

Modulus

Relational operators

◦ Same as C

◦ a < b, a > b, a <= b, a >= b

◦ 1-bit result: 0 if false, 1 if true

Equality operators

◦ a == b

◦ a != b

◦ Compared bit-by-bit

◦ 1-bit result: 0 (false), 1 (true)

Logical operators

operator Description

!

Logical

negation

&&

Logical and

||

Logical or

Bit-wise operators

operator

Description

~

NOT

&

AND

|

OR

^

XOR

^~ or ~^

XNOR

•

Shift

– Left shift <<

– Right shift >>

•

Concatenation

– {2’b10, 2’b01} equals 4’b1001

– reg

A =

B =

C =

C =

A,B,C;

1'b0;

2'b11;

{B,A};

{A,B};

Will these operations give different results?

Conditional Operators

◦ Conditional_expression ? True_expr : false expr

Example:

◦ x = 0; q = 0

◦ (if x < 0) ? (q = 0) : (q = 1);

Part 2

•

•

•

Executes loop over and over

Can only assign to registers in always blocks

2 types

– Level triggered - latch

– Edge triggered – flip-flop

always @ (posedge Clk) begin

if (Reset) begin

data <= 0;

end

else begin

data <= q_in;

end

end

•

Always blocks can be used for combinational

logic too

always @ (*) begin

case (Select)

2'b00: out <= A;

2'b01: out <= B;

2'b10: out <= C;

2'b11: out <= D;

endcase

end

Sequential assignment inside block

◦ Remember, this is HARDWARE

◦ Example:

assume A=B=0 before always block executes

always @ (posedge Clk) begin

A <= 1;

B <= A;

end

What will B equal after always block execution?

Can only be assigned to wires

assign A = B^Y;

assign C = Sel ? TrueVal : FalseVal;

???

http://en.wikipedia.org/wiki/Fieldprogrammable_gate_array

http://www.asicworld.com/verilog/intro1.html#Introduction

http://en.wikipedia.org/wiki/Verilog

“Verilog – Representation of Number Literals”,

http://web.engr.oregonstate.edu/~traylor/ec

e474/lecture_verilog/beamer/verilog_number

_literals.pdf