Introduction to Basys 2

Switches

Slide switches

Push button switches

Definition of Pin Number

The pin number of each

LED outputs

File: basys2.ucf

Used during implementation stage

Slide switches

Pushbutton

switches

Software

• Adept Active HDL is used for writing

Verilog code

• ISE/Webpack from Xilinx

– Purpose: create a “bit” file from a Verilog file

or schematic based source files

– The “bit” file is used to configure the basys2

board before it can perform any useful

functions.

• Adept can be used to configure the

FPGA with any suitable bit file stored on

the computer

Start Aldec Active-HDL Student

Edition

Start a New Workspace

New Design Wizard

Synthesis/Implementation Paths

We will use verilog in this class

Choose Default HDL Language

to Verilog

Design Name

Set Paths for Integrated Tools

Design Entry

Verilog File

Keyword: module/endmodule

The keywords module and endmodule

encapsulate the text that describes the module

Comments

• A pair of slashes

– // comment

– Forms a comment from the text that

follows it on the same line

• /*

*/

– /* comment */

Direction of the Signals

The direction of the input and output signals is given by

input, outout or inout (for a bi-directional signal)

There are 6 outputs as an array

Z[5:0]!

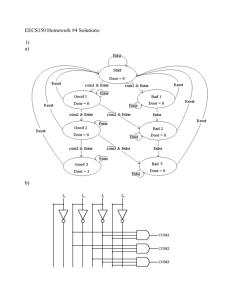

Schematic of Gates2

Concurrent Statements

To describe the output each gate, we simply write the logic

Equation for that gate preceded by the keyword assign.

The concurrent statements are statements that can be

written in any order.

wire

You can think of a wire as a wire in a circuit where actual voltages

Could be measured.

Compile

Simulate gates2.v

Create a Top-Level Test Bench

You need to create a top-level test bench so you can

use physical switches/push buttons to stimulate the design

Top-Level Verilog Test Bench

Top-Level Synthesis Option

Input and output signals are assigned to pins on the FPGA during synthesis.

Synthesize

Error Message During

Implementation Stage

Solution: incorrect Netlist

Implementation Completed

with No Error

Adept Interface

Example 1

Example 2

Start Another Design

Use Push Buttons to control LED

Platform Flash

Adept can also program a bit file into an on-board non-volatile ROM called

“Platform Flash”.

Once programmed, the Platform Flash can automatically transfer a stored bit

file to the FPGA at a subsequent power-on or reset event if the Mode Jumper

(JP3) is set to ROM.

The FPGA will remain configured until it is reset by a power-cycle event. The

Platform Flash ROM will retain a bit file until it is reprogrammed,

regardless of power-cycle events.

0

0