Homework2

advertisement

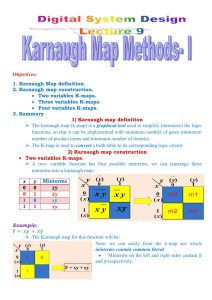

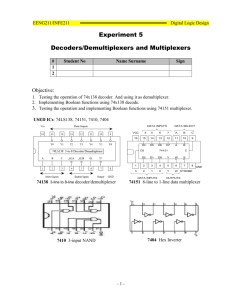

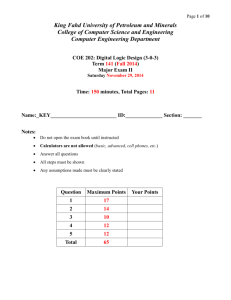

CS207 Fall 2001 Solution Homework 2 Exercise 1 A half adder is a two-input, two-output logic circuit used for adding two binary digits A and B without a carry-in. 1) Give a truth table for the output S and the carry-out C. 2) Implement S and C using: a. And, OR, Not, X-OR gates b. Nand gates only c. 2-to-1 MUX d. 2-to-4 decoders e. 3-to-8 decoders Solution: Let X, Y be the binary bits and S and C the sum and carry respectively. The truth table and logic expressions of the half adder are given by: X Y S C 0 0 1 1 0 0 0 1 0 1 0 1 0 1 1 1 S = X XOR Y = X'Y + XY' C = XY a) Draw the circuit (no major difficulty) b) Use De Morgan's law, to identify the Nand gates. You can implement NOT gates with Nand gates. c) Implementation of S, C using 2-to-1 MUX Y 0 Y' 1 2-1 MUX X S 0 0 Y 1 2-1 MUX X C d) Implementation of S, C using 2-to-4 decoder 00 01 10 11 X Y S C 2-to-4 Decoder e) Implementation of S, C using 3-to-8 decoder 0 000 001 010 011 X Y S C 100 101 110 111 3-to-8 Decoder Exercise 2 1. To determine a simplified expression for F(A,B,C,D) = (2,3,8,9) + d(10,11,12,13,14,15), draw a K-map for F (d's are don't care values): AB 00 01 11 10 d 1 CD 00 d 01 11 1 1 10 1 d d d d a) Implement F using And, OR, Not gates From the K-map above, a simplified expression of F is given by F = A + B'C and the corresponding circuit is given by: A F B C b) To implement F with 2-to-4 decoders, first use 2-to-4 decoders inn cascade to design a 4to-16 decoder. Next, or the 4 variables minterms corresponding to F. So we need to Or minterms 2,3,8 and 9 from the 4-to-16 decoder. Exercise 3 1. We want to find a minimal sum of product expression for F = A'B' + B'C' + AC + AB + BC. First, we draw a truth for F and use the table to get the K-map. I will just give the K-map representation (verify this, to make sure there is no mistake) : AB 00 01 11 10 1 0 1 1 1 0 1 1 1 1 1 1 1 1 1 CD 00 01 11 10 1 F = A + B' + C . 2. Using Karnaugh maps, find a minimal sum of products expression for the Boolean functions F1(A,B,C,D) and F2(A,B,C,D). Indicate the distinguished 1-cell on the maps and list the essential prime implicants of each function. F1(A,B,C,D) = (0,1,2,8,11) + d(3,9,15) F2(A,B,C,D) = (1,2,4,7,8,11,13,14) Solution Get a K-map for F1: AB 00 01 11 10 CD 1 1 * 00 1 01 11 d d d 1 10 1* * : distinguished cells The distinguished cells are the following minterms: m2, m8 All the prime implicants are essential. Function F is defined by the following minimal sum of products expression: F1 = A'B' + B'C' + ACD Get a K-map for F2: AB 00 01 11 10 CD 01 1 * 11 10 * 1 * 00 1 * 1 1 * 1 * 1* * 1 * : distinguished cells I don't see much hope here. It looks like all the cells are distinguished minterms. F2 cannot be simplified (unless I made a mistake in drawing the K-map). 3. Implement the minimal SOP of F1 and F2 using a PLA with 4 input variables, 8 products and 3 output. Solution: Note that even though F1 and F2 share minterms 1,2,8 and 11, we need a total of 9 distinct minterms (those of F2 and minterm m0 for F1). So we will use a PLA (programmable logic array) for each logic function (too bad for minterm sharing). The PLA implementations of F1 and F2 are: A B C D Do the same for F2. All product terms will be used…… . F1