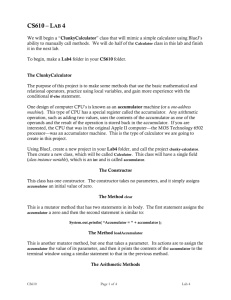

Von Neumann Architectures and the PDP-8

advertisement

Von Neumann Architectures and the PDP-8 A computer is an electronic (?) device operating under control of instructions stored in its own memory unit (stored program concept) • that accepts data (input) • processes data arithmetically and logically • displays information (output) from the processing and/or • stores the results for future use. The von Neumann Model • The von Neumann model consists of five major components: (1) input unit; (2) output unit; (3) arithmetic logic unit; (4) memory unit; (5) control unit. Source: Computer Architecture and Organization by M. Murdocca & V. Heuring Fig 1-13 page 10 The System Bus Model • A refinement of the von Neumann model, the system bus model has a CPU (ALU and control), memory, and an input/output unit. • Communication among components is handled by a shared pathway called the system bus, which is made up of the data bus, the address bus, and the control bus. There is also a power bus, and some architectures may also have a separate I/O bus. Source: Computer Architecture and Organization by M. Murdocca & V. Heuring Fig 1-14 page 10 Seven Properties of Von-Neumann Architectures G. Blaauw and F. Brooks on page 589 of their book Computer Architecture - Concepts and Evolution list seven "salient features" of von-Neumann architectures as proposed in the 1946 paper "Preliminary discussion of the logical design of an electronic computing device" by A. Burks, H. Goldstine, and J. von Neumann. 1. 2. 3. 4. 5. 6. 7. Single stream of instructions sequenced by instruction counter Instructions stored with data in addressable memory Instructions encoded as numbers - modifiable by arithmetic operations Radix 2 (binary) Word length long enough for scientific computation Single Address - single operation instructions Single Accumulator with MQ Register Stored Program Concept: 1. Instructions stored with data in addressable memory 2. Instructions encoded as numbers - modifiable by arithmetic operations Addressable Memory: 1. Memory accessed by its numeric address (location in memory) 2. Distinction between address of memory and contents at that address Studying Computer Architecture: We look at three things • Memory: How is memory structured/organized? What is the size in bits of the smallest addressable cell in memory? Is memory word addressable or byte addressable. What is the memory address space (size of memory)? How are physical addresses obtained from logical addresses? • Processor/CPU: Registers: size and number, general purpose vs. special purpose. What ALU operations are supported? • Instruction Set: What is the instructions mix? What is the instruction format and how many are there? What addressing modes are supported? The instruction set defines the architecture. The PDP-8 Introduced in 1965 by Digital Equipment Corp. (DEC) – priced at $18K (cheap!) Transistor technology (2nd generation technology) Considered/marketed as a “mini-computer” 12–bit word-addressable; 4096 words of memory; 8 op-codes 16 bit byte-addressable very successful PDP-11 was the (market) successor The PDP-8 Emulator Program PDP-8 Bits Words and Integer Representation 12 bit words – bit numbering left to right msb-> <-lsb +---+---+---+---+---+---+---+---+---+---+---+---+ 0 1 2 3 4 5 6 7 8 9 10 11 normally represented in octal binary Octal binary octal 000 0 100 4 001 1 101 5 010 2 110 6 011 3 111 7 Organization of PDP-8 Memory 4096 (212) words 12 bit physical addresses memory organized into 32 pages of 128 words page/offset logical addressing scheme bits 0 – 4: page; bits 5 – 11: offset 5. zero page /current page addressing 1. 2. 3. 4. PDP-8 Registers 1. 12 bit accumulator 2. 1 bit link register for carry out +---+ | | +---+ Link +---+---+---+---+---+---+---+---+---+---+---+---+ | | | | | | | | | | | | | +---+---+---+---+---+---+---+---+---+---+---+---+ Accumulator 1. 12 bit PC (program counter) holds address of next instruction 2. 3 bit IR (instruction register) holds current op-code 3. 12 MQ register – needed for multiplication/division 4. 12 bit Central Processor Memory Register (CPMA) holds address to access memory 5. 12 bit Memory Buffer Register (MB) – hold contents of memory access Input/Output 1. It’s complicated • • Problem of data format conversion How do you synchronize a fast CPU with a slow I/O device? 2. Restricted to reading and writing single ASCII characters 3. Uses busy waiting loop 4. Keyboard and printer (TTY device) have data buffers and 1-bit ready flag for synchronization PDP-8 Instructions Memory Reference Instructions 0 1 2 3 4 5 6 7 8 9 10 11 +---+---+---+---+---+---+---+---+---+---+---+---+ | opcode |IA |MP | offset address | +---+---+---+---+---+---+---+---+---+---+---+---+ Opcode 6 (I/O) Instructions 0 1 2 3 4 5 6 7 8 9 10 11 +---+---+---+---+---+---+---+---+---+---+---+---+ | 1 | 1 | 0 | device number | function | +---+---+---+---+---+---+---+---+---+---+---+---+ Opcode 7 Microinstructions (3 sub-groups) 0 1 2 3 4 5 6 7 8 9 10 11 +---+---+---+---+---+---+---+---+---+---+---+---+ | 1 | 1 | 1 ||0 |CLA|CLL|CMA|CML|RAR|RAL|0/1|IAC| +---+---+---+---+---+---+---+---+---+---+---+---+ Where individual bits control micro-functions Addressing Modes MRI instructions Effective Address (Eaddr) = Address of Operand 1. Zero Page Addressing • EAddr = 00000 + offset 2. Current Page Addressing • EAddr = Instr Address [0…4] + offset 3. Indirect Addressing 4. Auto-Indexing PDP-8 Seven Properties of Von-Neumann Architectures Recall the seven Blaauw and Brooks "salient features" of vonNeumann architectures 1. Single stream of instructions sequenced by instruction counter 2. Instructions stored with data in addressable memory 3. Instructions encoded as numbers - modifiable by arithmetic operations 4. Radix 2 (binary) 5. Word length long enough for scientific computation 6. Single Address - single operation instructions 7. Single Accumulator with MQ Register PDP-8 as Von Neumann Architecture Memory Unit MAR kbd buffer ready flag Keyboard MBR AC print buffer MQ ? L ? ALU PC IR Control Unit ready flag Printer Machine language coding the PDP-8 12-bit Two’s Complement Binary Representation +---+---+---+---+---+---+---+---+---+---+---+---+ | s | b | b | b | b | b | b | b | b | b | b | b | +---+---+---+---+---+---+---+---+---+---+---+---+ where s has weight -211 000 000 000 000 000 000 000 000 000 000 000 000 000 001 010 011 = = = = 0 1 2 3 111 111 111 111 111 111 111 111 111 111 111 111 111 110 101 100 = = = = -1 -2 -3 -4 Nine PDP-8 Machine Codes 1 Twos Complement Add (Load Accumulator) 2 Increment and Skip (Next Instruction) if Zero 3 Deposit and Clear Accumulator 5 Jump 7041 Negate Accumulator 7300 Clear Accumulator and Link 7402 Halt 7500 Skip Next Instruction if Accumulator is Negative 7510 Skip Next Instruction if Accumulator is Positive