Lec4a_SAP1

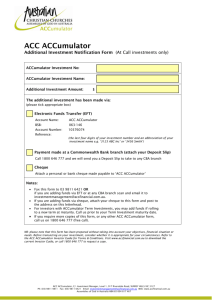

advertisement

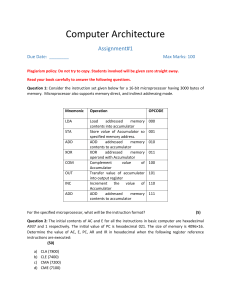

SAP1 (Simple-As-Possible) Computer 1 Architecture • Program counter – 4-bit wide • Input & MAR – Includes the address & data switch registers – Send 4 address bits and 8 data bits to the RAM • RAM – 16 x 8 • Instruction Register – Loads the content of the addressed memory location through the W bus – Upper nibble goes directly to the ControllerSequencer – Lower nibble is read onto the W bus when 2 needed Architecture • Controller-Sequencer – Before each computer run • CLR’ signal sent to PC –resets the program counter to 0000 • CLR signal sent to IR – wipes out the last instruction in the IR • CLK signal sent to all buffer registers – synchronizes the operation of the computer • CLK’ signal to PC – The 12 bits that comes out controls the rest of the computer – The 12 wires carrying the control word is called control bus 3 4 Architecture • Control word format CON = CP EP L’M CE’ L’I E’I L’A EA SU EU L’B L’O – This word determines how the registers will react to the next positive CLK edge – Ex. EP = high, L’M = low – mean that the contents of PC are latched into the MAR on the next (+) clock edge – Ex. CE’ = low, L’A = low – mean that the addressed RAM word will be transferred to the accumulator on the next (+) clock edge 5 Architecture • Accumulator – Buffer register – 8-bit wide – When EA is high, the content appears on the W bus • Adder-Subtracter – – – – 2’s complement adder-subtracter When SU is low, S = A + B When SU is high, S = A + B’ When EU is high, the content appears on the W bus 6 Architecture • B Register – Another 8-bit wide buffer register – Used in arithmetic operations – When L’B is low & (+) clock edge, the word on the W bus will be loaded • Output Register – Often called the output port – When EA is high & L’O is low , the next (+) clock edge loads the accumulator word into the output register • Binary display – Row of 8 LEDs – Each LED connects to 1 flip-flop (FF) of the output port 7 Architecture • Control Unit – PC – Controller-Sequencer – IR • ALU – Accumulator – B register – Adder-subtracter •Memory –MAR •I/O unit –Input programming switches –Output port –Binary display 8 Instruction Set • LDA – Load the accumulator – Ex LDA 5H (R5 = 1010 1111) • A = 1010 1111 • ADD – Ex ADD 3H • Adds the content of memory location 3H to the accumulator content, save the result to the accumulator • Content of R3 is loaded to B 9 Instruction Set • SUB – Ex SUB 2H • Subtracts the content of memory location 2H from the accumulator content, save the result to the accumulator • Content of R3 is loaded to B • OUT – Transfer the accumulator content to the output port • HLT – Tells the computer to stop processing data 10 Instruction Set • Memory-reference instructions – LDA, ADD, SUB • Not Memory-reference instructions – OUT, HLT • Mnemonics – abbreviated instructions • SAP1 – upward compatible with the 8080/8085 instruction set 11 Fetch Cycle T1 – address state - the address from PC is transferred to MAR CON = CP EP L’M CE’ =0 1 0 1 L’I E’I L’A EA 1 1 1 0 SU EU L’B L’O 0 0 1 1 T2 – increment state - PC +1 CON = CP EP L’M CE’ =1 0 1 1 L’I E’I L’A EA 1 1 1 0 SU EU L’B L’O 0 0 1 1 12 Fetch Cycle T3 – memory state - the addressed RAM instruction is transferred from the memory to IR CON = CP EP L’M CE’ =0 0 1 0 L’I E’I L’A EA 0 1 1 0 SU EU L’B L’O 0 0 1 1 13 Execute Cycle LDA Routine – ex LDA 9H IR = 0000 1001 T4 – 0000 goes to the controller-sequencer - 1001 goes to the MAR - the addressed RAM instruction is transferred from the memory to IR CON = CP EP L’M CE’ =0 0 0 1 L’I E’I L’A EA 1 0 1 0 SU EU L’B L’O 0 0 1 1 T5 – the addressed data word will be loaded to the Accumulator CON = CP EP L’M CE’ =0 0 1 0 L’I E’I L’A EA 1 1 0 0 T6 – no operation state SU EU L’B L’O 0 0 1 1 14