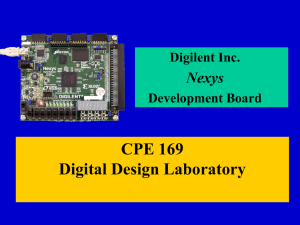

CoolRunner-II Design Kit Digilent Board Description

advertisement

Design Kit CoolRunner-II RealDigital CPLDs • Advanced .18 process technology • JTAG In-System Programming Support – IEEE 1532 Compliant • Advanced design features – Multiple I/O standards – Multiple I/O banks – Input hysteresis – Extra clocking modes • New enhanced architecture allows design flexibility – 16 macrocells per function block – Global signals available at each macrocell – New DataGATE and CoolCLOCK features • Patented full-CMOS circuitry runs at extremely low power without compromising performance – Very low Static Icc Design Kit • A complete, easy to use CoolRunner-II CPLD design kit for: – Logic designers new to CPLDs – CPLD designers new to Xilinx – ASIC designers not aware of CoolRunner-II advanced features • Simple and inexpensive demo board ready to use – – – – – – – Preprogrammed CPLD which flashes LED on power up Battery or AC outlet power source Inexpensive cable for programming LED's for simple testing Dual in line I/O header for easy connections Jumpers for easy modifications Multiple device selection on a single board (CR-II or XC9500XL/XV) CoolRunner-II Design Kit • Main box contains: – Digilent CoolRunner-II PCB populated with – XC2C256-7TQ144C and XC9572XL-10VQ44C – Parallel printer download cable – Also supported are HW-PC3/4 and Digilent JTAG3 cable – WebPACK CD – Full up design & programming software – Resource CD – Presentations, data sheets & technical information – Beginner’s Logic Design Book – AA battery holder Digilent Board Description • Populated with – IC1 • XC9572XL-10VQ44C – IC2 • XC2C256-7TQ144C Digilent Board Description • JTAG connection for programming CPLD Digilent Board Description • Extra features – Pushbutton switch – LED's – Wall wart AC connection Digilent Board Description • 18-hole by 46 hole breadboard area for external component mounting • Dual-in-line header for easy connection to CPLD I/Os – IC1 port C – IC2 ports A, B, D C D B A Digilent Board Description • Power jumpers – JP1 • Battery or unregulated supply – J8 • • • • VIO2 VCORE VIO1 Ground – JP2,3,4 • Battery mode • Wall-plug mode • External mode Digilent Board Description • Device Selection – JP 7, 8 • IC1 or IC2 or both • JTAG Programming – JP 6,9, JP 5,10 • Diagram of JTAG jumper settings Collateral • Resource CD – – – – – – Digilent board schematics, reference manual Reference designs (link) Application notes (link) Data sheets (link) Presentations White papers • Ready to use WebPACK design software – HDL or schematic designs – HDL bencher – Simulation with ModelSIM Online Software Solutions • Free ISE WebPACK™ – – – – – – Downloadable desktop solution HDL / ABEL synthesis & simulation JTAG & 3rd party EDA support Supports all Xilinx CPLD families Supports Spartan-II, IIE & III, Virtex-E & II (up to 300K gates) FPGAs Links to online purchasing • Free WebFITTER™ – – – – – Easily fit designs for all Xilinx CPLDs online Accepts VHDL/verilog/abel & standard netlists Simple PLD & competitive conversions Fitting & timing reports Online price quotes for purchasing the best PLD silicon solution Conclusion • CoolRunner-II design kit offers an inexpensive method to test designs – 2 CPLDs with over 320 available Macrocells (XC2C256 and XC9572XL) – Breadboard area • Maximum flexibility for other uses – I/O header for ease of connections for daughter cards – LED's • Functional test and user programmable – Pushbutton switch • Basic reset switch