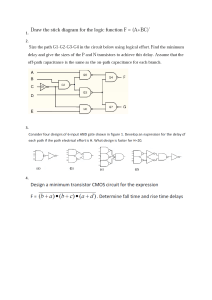

Assignment 1 Complex CMOS logic circuit Layout Design 1. Implement the equation X = ((A + B) (C + D + E) + F) G using complementary CMOS. Size the devices so that the output resistance is the same as that of an inverter with an NMOS W/L = 2 and PMOS W/L = 6. Which input pattern(s) would give the worst and best equivalent pull-up or pull-down resistance? 2. Implement the following expression in a full static CMOS logic fashion using no more than 10 transistors: 3. Consider the circuit of Figure. a. What is the logic function implemented by the CMOS transistor network? Size the NMOS and PMOS devices so that the output resistance is the same as that of an inverter with an NMOS W/L = 4 and PMOS W/L = 8. b. What are the input patterns that give the worst case tpHL and tpLH. State clearly what are the initial input patterns and which input(s) has to make a transition in order to achieve this maximum propagation delay. Consider the effect of the capacitances at the internal nodes. c. Verify part (b) with SPICE. Assume all transistors have minimum gate length (0.25mm).d. If P(A=1)=0.5, P(B=1)=0.2, P(C=1)=0.3 and P(D=1)=1, determine the power dissipation in the logic gate. Assume VDD=2.5V, Cout=30fF and fclk=250MHz. d. Draw the layout for the above schematic. 4. CMOS Logic a. Do the following two circuits implement the same logic function? If yes, what is that logic function? If no, give Boolean expressions for both circuits. b. Will these two circuits’ output resistances always be equal to each other? c. Will these two circuits’ rise and fall times always be equal to each other? Why or why not? 6. Consider the logic expression Y= (a+b).((c.d)+e) .construct the nFET array for the logic. Apply bubble pushing to obtain the pFET logic and hence obtain the pFET array. Draw the layout for it. 7. Implement the Boolean function F = (a+b).(a+c).(b+d) using CMOS logic transistors. 8. Implement the logic expression Y= A.(D+C)+C.E using the basic CMOS NAND circuitry. 9. A pMOS transistor has W/L=10 with process parameters k’ = 30μA/V and Vtp = -0.6V. 2 p For each of the cases below, identify the region of operation (cutoff, triode, saturation). Assume V = 0V and VDD = 3V. SB a) V = 1V, V = 3V b) V = 3V, V = 2V SG SG c) 10. V SD SG SD = 0.5, V SD = 1V -1 A pMOS transistor with a channel length modulation factor of λ=0.05V is sized so that it has a drain current of I =15μA when V = V -|Vtp|. D SD SG a) Accounting for channel length modulation what is the drain current if the drain voltage V drops by 2.5V? Note: you do have all the information needed. D b) Recognizing that the output resistance is defined as the change in drain voltage relative to the change in drain current, calculate the output resistance in the saturation (active) region.