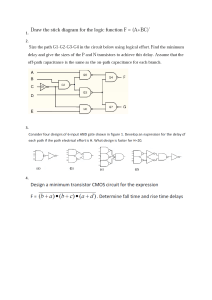

Integrated Circuits – Introduction to VLSI (046237) Includes slides adapted from Digital Integrated Circuits, by J. Rabaey et al., from CMOS VLSI design: a circuits and systems perspective (4th ed.) by N. Weste and D. Harris, and from Penn State CSE477, MIT 6371 and Stanford 313 VLSI courses. Logistics • Eduardo Maayan – eduardo.maayan@infineon.com - 054-4968387 • Assignments and grading – • Homework assignments (15%) – There will be a total of 12-13 “dry” homework assignments. Only 2 specific HWs (out of the 13) should be submitted (in pairs) and will be graded (15% of the final grade). The other 10-11 HW assignments are for self-work, should not be submitted and will not be graded. • Lab assignments (35%) – There will be 2 lab assignments to be performed in the VLSI Lab. These should be submitted in pairs and will be graded. Lab #1 (25%): Design, layout and simulation of a logic gate, characterization and design verification. Lab #2 (10%): Backend design flow of a system (given in RTL): synthesis, delay/power/area optimization, floor-planning, partitioning, place and route and other backend steps, design verification. • Final exam (50%) – The exam will be styled like exams from previous semesters and like dry homework questions. p.2 Logistics • Textbooks – p.3 What is a VLSI circuit? p.4 What is a VLSI circuit? p.5 Why VLSI ? 1. More attractive than non-integrated circuits • • • • • Smaller circuits (size) Lower cost Better performance (speed/power) Higher reliability Enables unique design architectures 2. Along the past 60Y, the VLSI devices dimensions are being constantly scaled down. The outcome: • # of transistors constantly Increases • The cost (of a function) is constantly reduced • Performance / functionality constantly improves • Business growth & $$ generator 2022 p.6 The Transistor Revolution First transistor Bell Labs, 1948 • Bell Labs lays the groundwork: • 1940: Russel Ohl develops PN junction which produces 0.5V when exposed to light. • 1945: Bell sets up lab in the hopes of developing “solid state” components to replace existing electromechanical systems. William Schockley, John Bardeen, Walter Brattain: all solid-state physicists. Focus on Si and Ge. • 1947: Bardeen and Brattain create point-contact transistor w/ two PN junctions. Gain = 18. (U.S. Patent 2,524,035) • Announced in July 1948. But treated as a novelty until 1951 invention of the junction transistor. Bell Labs willing to license the rights to the transistor to any company for a royalty (which was waived for hearing aid companies as a gesture to Alex. G. Bell). • Transistor was good: smaller, faster, more reliable and economical but this is only half the story since the circuits, albeit smaller, were still constructed in much the same way. p.9 The Transistor Revolution • 1951: Shockley develops the junction transistor which can be manufactured in quantity (U.S. Patent 2,623,105). • 1952: GWA Dummer forecasts “solid block [with] layers of insulating, conducting and amplifying materials” • 1954: The first transistor radio! Also, TI makes first silicon transistor (price $2.50) • 1956: Bardeen, Shockley, Brattain receive Nobel Prize. p.10 Early Integration • Jack Kilby was denied entry to MIT because of poor high school grades … Kilby worked on miniaturized components during the war and experimented with photolithography. Went to 1952 Bell Labs transistor course. • High labor costs at TI got Kilby thinking about “solid circuits” over the July 1959 plant closing. Built phase-shift oscillator and it worked on 9/12/59. By the end of the year, he had constructed several examples, including the flip-flop shown in the patent drawing above. Components are connected by hand-soldered wires and isolated by “shaping” and PN diodes used as resistors. • In December 2000, Kilby was awarded the Nobel Prize in physics for this work. p.11 Making it real ... • After getting his PhD in 1953 (MIT), Robert Noyce joined Shockley Semiconductor Labs in 1955. In 1957, Noyce left Shockley’s lab (Schockley wasn’t the best of managers ...) to form Fairchild Semiconductor with Jean Hoerni. Gordon Moore is another founder. • In early 1958, Hoerni invents a technique for diffusing impurities into the silicon to build planar transistors and then using a SiO2 insulator. In spring of 1959, Kurt Lehovec at Sprague Elec. Co. in North Adams, MA invents isolation technique using back-to-back pn junctions. • In mid 1959, Noyce develops first true IC using planar transistors, back-to-back pn junctions for isolation, diode-isolated silicon resistors and SiO2 insulation wired using his innovation: using metal deposited by evaporation through a mask to form the interconnect -- keeping the IC flat and easy to build. p.12 The First Integrated Circuits Bipolar logic - 1960’s Fairchild bipolar RTL Flip-Flop 1961: TI and Fairchild introduced the first logic IC’s (cost ~$50 in quantity!). This is a dual flip-flop with 4 transistors + 5 resistors. 1962 : Fairchild IC p.13 The First Integrated Circuits 1963: Densities and yields are improving. This circuit has two logic gates, each composed of four transistors and an equal number of resistors. 1964 : First MOS IC (RCA) p.14 The First Integrated Circuits 1967: Fairchild markets this semi-custom chip – The “Micromosaic” IC. Transistors (organized in columns) could be easily rewired using a two-layer interconnect to create different circuits. Final Al layer of interconnect could be customized for different applications This circuit contains ~150 logic gates. Masks are laid-out, cut and checked by hand… Beginning of a design flow but no computer automation yet. p.15 The First Integrated Circuits – Also Memories 1966: Robert Dennard invents 1-T DRAM at IBM TJ Watson Research Center. 1970: 256b Static & 1Kb Dynamic RAM 1971: Dov Frohman’s UV-erasable EPROM UV-erasable EPROM p.16 INTegrated ELectronics = Intel 1968: Noyce and Moore leave Fairchild and found Intel. No business plan, just a promise to specialize in memory chips. They and Art Rock raise $2.5M in two days and move to Santa Clara. By 1971 Intel had 500 employees; by 2020 it had >110,000 employees and >$77B in sales. In 1971 Intel introduces the first microprocessor, designed by Ted Hoff. The 4004 had 4-bit buses and a clock rate of 108KHz. It had 2300 PMOS transistors and was built in a 10u process. It never captured much interest in the market and was soon eclipsed by its more capable brethren. p.17 VLSI Technology – Historical transitions Pros Cons Bipolar Area PMOS Area & Performance NMOS Performance (Process cost) Power (Area & cost) Performance (Process cost) NMOS enh./dep. CMOS BiCMOS Power CMOS p.18 INTegrated ELectronics = Intel 1968: Noyce and Moore leave Fairchild and found Intel. No business plan, just a promise to specialize in memory chips. They and Art Rock raise $2.5M in two days and move to Santa Clara. By 1971 Intel had 500 employees; by 2019 it had >100,000 employees and >$72B in sales. In 1971 Intel introduces the first microprocessor, designed by Ted Hoff. The 4004 had 4-bit buses and a clock rate of 108KHz. It had 2300 PMOS transistors and was built in a 10u process. It never captured much interest in the market and was soon eclipsed by its more capable brethren. What does it mean? p.19 A ”XX process” – What does it mean? (”XX” = 10um 50Y ago and <10nm nowadays) Planar MOS transistor cross section In the (already quite far) past “XX” typically referred to the min transistor Ldrawn or Leff or Half transistor pitch OR to F = Half of the Min line pitch (F is the Technology Feature Size). p.20 A ”XX process” – What does it mean? (”XX” = 10um 50Y ago and <10nm nowadays) Nowadays it may be considered as some “equivalent planar version node” required to achieve the scaled down area p.21 INTegrated ELectronics = Intel 1968: Noyce and Moore leave Fairchild and found Intel. No business plan, just a promise to specialize in memory chips. They and Art Rock raise $2.5M in two days and move to Santa Clara. By 1971 Intel had 500 employees; by 2019 it had >100,000 employees and >$72B in sales. In 1971 Intel introduces the first microprocessor, designed by Ted Hoff. The 4004 had 4-bit buses and a clock rate of 108KHz. It had 2300 PMOS transistors and was built in a 10u process. It never captured much interest in the market and was soon eclipsed by its more capable brethren. p.22 8008 & 8080 Introduced in 1972, the 8008 had 3,500 PMOS transistors supporting a byte-wide data path. Despite its limitations, the 8008 was the first microprocessor capable of playing the role of computer CPU as demonstrated on the cover of the July ‘74 issue of Radio-Electronics. Introduced in 1974, the 8080 had 6,000 NMOS transistors fab’ed in a 6u process. The clock rate was 2Mhz, more than enough to ignite the personal computer industry. p.23 VLSI Technology – Historical transitions Pros Cons Bipolar Area PMOS Area & Performance NMOS Performance (Process cost) Power (Area & cost) Performance (Process cost) NMOS enh./dep. CMOS BiCMOS Power CMOS p.24 8086 / 8088 ⚫ 16-bit processor (1978-9) IBM PC and PC XT ⚫ Revolutionary products ⚫ Introduced x86 ISA Characteristics ⚫ 3mm process ⚫ 29k transistors ⚫ 5-10 MHz ⚫ 16-bit word size ⚫ 40-pin DIP package Microcode ROM ⚫ ⚫ ⚫ p.25 80286 ⚫ Virtual memory (1982) IBM PC AT Characteristics ⚫ 1.5mm process ⚫ NMOS enh./dep. ⚫ 134k transistors ⚫ 6-12 MHz ⚫ 16-bit word size ⚫ 68-pin PGA Regular datapaths and ROMs Bitslices clearly visible ⚫ ⚫ ⚫ p.26 80286 ⚫ Virtual memory (1982) IBM PC AT Characteristics ⚫ 1.5mm process ⚫ NMOS enh./dep. ⚫ 134k transistors ⚫ 6-12 MHz ⚫ 16-bit word size ⚫ 68-pin PGA Regular datapaths and ROMs Bitslices clearly visible ⚫ ⚫ ⚫ 8088 → 80286: 4Y scaling → x2 smaller lateral dimension → x4 smaller area OR x4 more transistors in the same area p.27 80286 ⚫ Virtual memory (1982) IBM PC AT Characteristics ⚫ 1.5mm process ⚫ NMOS enh./dep. ⚫ 134k transistors ⚫ 6-12 MHz ⚫ 16-bit word size ⚫ 68-pin PGA Regular datapaths and ROMs Bitslices clearly visible ⚫ ⚫ ⚫ p.28 VLSI Technology – Historical transitions Pros Cons Bipolar Area PMOS Area & Performance NMOS Performance (Process cost) Power (Area & cost) Performance (Process cost) NMOS enh./dep. CMOS BiCMOS Power CMOS p.29 80386 ⚫ 32-bit processor (1985) Modern x86 ISA Characteristics ⚫ 1.5-1 mm process ⚫ CMOS Technology ⚫ 275k transistors ⚫ 16-33 MHz ⚫ 32-bit word size ⚫ 100-pin PGA 32-bit datapath, microcode ROM, synthesized control ⚫ ⚫ ⚫ p.30 80386 ⚫ 32-bit processor (1985) Modern x86 ISA Characteristics ⚫ 1.5-1 mm process ⚫ CMOS Technology ⚫ 275k transistors ⚫ 16-33 MHz ⚫ 32-bit word size ⚫ 100-pin PGA 32-bit datapath, microcode ROM, synthesized control ⚫ ⚫ ⚫ “1.5-1um” refers to the fact that this new uP architecture was 1st manufactured at 1.5um and then migrated to 1um (~x0.7 scaling factor = 0.5 Area). p.31 80386 ⚫ 32-bit processor (1985) Modern x86 ISA Characteristics ⚫ 1.5-1 mm process ⚫ CMOS Technology ⚫ 275k transistors ⚫ 16-33 MHz ⚫ 32-bit word size ⚫ 100-pin PGA 32-bit datapath, microcode ROM, synthesized control ⚫ ⚫ ⚫ p.32 VLSI Technology – Historical transitions Pros Cons Bipolar Area PMOS Area & Performance NMOS Performance (Process cost) Power (Area & cost) Performance (Process cost) NMOS enh./dep. CMOS BiCMOS Power CMOS p.33 80486 ⚫ Pipelining (1989) Floating point unit ⚫ 8 KB cache Characteristics ⚫ 1-0.6 mm CMOS process ⚫ 1.2M transistors ⚫ 25-100 MHz ⚫ 32-bit word size ⚫ 168-pin PGA Cache, Integer datapath, FPU, microcode, synthesized control ⚫ ⚫ ⚫ p.34 Pentium ⚫ ⚫ ⚫ Superscalar (1993) ⚫ 2 instructions per cycle ⚫ Separate 8KB I$ & D$ Characteristics ⚫ 0.8-0.35 mm process ⚫ BiCMOS technology ⚫ 3.2M transistors ⚫ 60-300 MHz ⚫ 32-bit word size ⚫ 296-pin PGA Caches, datapath, FPU, control p.35 Pentium ⚫ ⚫ ⚫ Superscalar (1993) ⚫ 2 instructions per cycle ⚫ Separate 8KB I$ & D$ Characteristics ⚫ 0.8-0.35 mm process ⚫ BiCMOS technology ⚫ 3.2M transistors ⚫ 60-300 MHz ⚫ 32-bit word size ⚫ 296-pin PGA Caches, datapath, FPU, control Manufactured at 3 technology nodes – At the established 0.8um and then migrated twice (0.6 & 0.35um) p.36 Pentium ⚫ ⚫ ⚫ Superscalar (1993) ⚫ 2 instructions per cycle ⚫ Separate 8KB I$ & D$ Characteristics ⚫ 0.8-0.35 mm process ⚫ BiCMOS technology ⚫ 3.2M transistors ⚫ 60-300 MHz ⚫ 32-bit word size ⚫ 296-pin PGA Caches, datapath, FPU, control p.37 VLSI Technology – Historical transitions Pros Cons Bipolar Area PMOS Area & Performance NMOS Performance (Process cost) Power (Area & cost) Performance (Process cost) NMOS enh./dep. CMOS BiCMOS Power CMOS p.38 Pentium Pro / II / III ⚫ ⚫ Dynamic execution (1995-9) ⚫ 3 micro-ops / cycle ⚫ Out of order execution ⚫ 16-32 KB I$ & D$ ⚫ Multimedia instructions ⚫ PIII adds 256+ KB L2$ Characteristics ⚫ 0.6-0.18 mm process ⚫ CMOS Technology ⚫ 5.5M-28M transistors ⚫ 166-1000 MHz ⚫ 32-bit word size ⚫ MCM / SECC p.39 VLSI Technology – Historical transitions Pros Cons Bipolar Area PMOS Area & Performance NMOS Performance (Process cost) Power (Area & cost) Performance (Process cost) NMOS enh./dep. CMOS BiCMOS Power/Performance CMOS p.40 Pentium 4 ⚫ ⚫ ⚫ Deep pipeline (2001) ⚫ Very fast clock ⚫ 256-1024 KB L2$ Characteristics ⚫ 180- 65nm CMOS process ⚫ 42-125M transistors ⚫ 1.4-3.4 GHz ⚫ Up to 160 W ⚫ 32/64-bit word size ⚫ 478-pin PGA Units start to become invisible on this scale p.41 VLSI Technology Evolution Technology: Bipolar → PMOS → NMOS → Planar CMOS → BiCMOS → CMOS → LowK/Strain/HKMG CMOS→ Non-planar CMOS → … Min. Feature Size: 10um … 1.5um … 0.5um … 0.18um … 0.13um ... 90 ... 45 … 32 ... 22 ... 14 ... 10 … 7 … 5nm … Supply Voltage: 5→ 3.3 → 2.5 → 1.8 → 1.5 → 1.2 → 1.0 → 0.9 → 0.7 → … p.42 Moore’s Law: Then … • 1965: Gordon Moore plotted the # of transistors on each chip • Fit straight line on semilog scale • X2 Transistor count every ~26 months [Moore65] Electronics Magazine p.43 Moore’s Law: Then & Now • Gordon Moore’s trend is maintained along >50Y for both Logic & Memory ICs p.45 Feature Size ⚫ Minimum feature size shrinking 30% every 2-3 years p.46 Corollaries • Many other factors grow exponentially • Ex: clock frequency, processor performance p.47 Will Moore’s Law end ? • Will Moore’s Law run out of steam? • Many reasons have been predicted for end of scaling • Dynamic power • Subthreshold leakage, tunneling • Short channel effects • Fabrication costs • Electromigration • Interconnect delay • etc. etc. … • Rumors of demise have been exaggerated p.51 Will Moore’s Law end ? p.52 Gordon Moore’s Presentation in ISSCC 2003 Page 1 Last Page The presentation is available in the course website p.53 Will Moore’s Law end ? p.54 Will Moore’s Law end ? p.55 Will Moore’s Law end ? p.56 Will Moore’s Law end ? p.57 What changed in VLSI along 50Y? • Scaling continues driven by demand, cost, functionality, performance. • Till early 2000’s the focus was mainly on faster devices, running at higher and higher clock frequencies. • Intel VP Patrick Gelsinger (ISSCC 2001): “If scaling continues at present pace, by 2005, high speed processors would have power density of nuclear reactor, by 2010, a rocket nozzle, and by 2015, surface of sun. Business as usual will not work in the future.” • Attention to power is a must [Intel] p.58 What changed in VLSI along 50Y? [Intel] p.59 Actual Data Itanium Temperature Plot • Temperature must be well controlled → On-die Temperature detector. • Design Verification must take into account the actual die temp. + the temp. gradient on die • Packaging & system must be designed to enable the heat dissipation. p.60 What happens when the CPU cooler is removed? http://www.youtube.com/watch?v=y39D4529FM4 p.61 The design objectives changed • The Tejas had been projected to run at 7 GHz, but it never did. It would get too hot … • So, Intel and others quickly changed direction, slowed down their processors, and announced dualcore/multicore, which became a standard nowadays. p.62 Low Power Design Innovation • Architecture + Circuit Design Techniques • Example: Atom ⚫ ⚫ ⚫ Low power CPU for netbooks ⚫ Pentium-style architecture ⚫ 512KB+ L2$ Characteristics ⚫ 45-32 nm process ⚫ 47M transistors ⚫ 0.8-1.8+ GHz ⚫ 1.4-13 W ⚫ 32/64-bit word size Low voltage (0.7-1.1 V) operation ⚫ Excellent performance/power p.63 From VLSI circuits to VLSI Systems • SoC Example – ➢ OMAP (Open Multimedia Applications Platform) System on Chip (SoC) for portable and mobile multimedia applications. p.64 Scaling • The only constant in VLSI is constant change • Feature size shrinks by 30% every 2-3 years • Transistors become cheaper • Transistors become faster and lower power • Wires do not improve as transistors (and may get worse) • With every generation can integrate 2x more functions on a chip. The chip cost does not increase significantly. • But … • How to design chips with more and more functions? • Design engineering population does not double every two years… • Hence, a need for more efficient design methods • Exploit different levels of abstraction p.65 Design Productivity Trends 100,000 Logic Tr./Chip 10,000 Tr./Staff Month. 1,000 100 58%/Yr. compounded Complexity growth rate 10 100 1 10 x 0.1 xx x x 0.01 x 1 21%/Yr. compound Productivity growth rate x x Productivity (K) Trans./Staff - Mo. 1,000 0.1 0.01 2009 2007 2005 2003 2001 1999 1997 1995 1993 1991 1989 1987 1985 1983 0.001 1981 Logic Transistor per Chip (M) Complexity 10,000 Complexity outpaces design productivity p.66 Design Abstraction Levels SYSTEM MODULE + GATE CIRCUIT DEVICE G S n+ D n+ p.67 Computer Aided Design (CAD) Tools p.68 Implementation strategies p.69 Design Strategies p.70 Implementation Strategies – Packaging Related p.71 Implementation Strategies – Multi-Die Packaging p.72 Fundamental Design Metrics • Functionality • Cost • NRE (fixed) costs - design effort • RE (variable) costs - cost of parts, assembly, test • Reliability, robustness • Noise margins and immunity • Failures screening • Performance • Speed (delay) • Power consumption; energy • Time-to-market VLSI Design The art of trade-offs • Scalability, Process migration p.73 Implementation metrics VLSI Design The art of trade-offs p.74