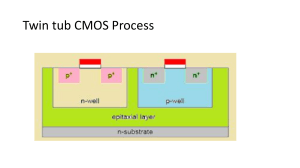

FACULTY OF ENGINEERING AND BUILT ENVIRONMENT MASTER OF SCIENCE IN ELECTRICAL & ELECTRONICS ENGINEERING MEE 1123 ADVANCED VLSI DESIGN ASSIGNMENT - 1 Name: S Mohamed Thouseef Stud ID: 01252304380 1 1. Introduction: CMOS stands for Complementary Metal Oxide Semiconductor. The CMOS process was originally conceived by Frank Wanlass. It is used to fabricate digital circuits and IC chips. CMOS is a type of metal–oxide–semiconductor field-effect transistor (MOSFET) fabrication process that uses a combination of NMOS (N-type Metal Oxide Semiconductor) and PMOS (P-type Metal Oxide Semiconductor) transistor pairs that are symmetrical. The phrase "metal–oxide–semiconductor" is a reference to the physical structure of MOS field-effect transistors, having a metal gate electrode placed on top of an oxide insulator, which in turn is on top of a semiconductor material. Aluminium was once used but now the material is polysilicon. The CMOS (complementary metal-oxide silicon) fabrication technology is recognized as the leader of VLSI systems technology. CMOS provides an inherently low power static circuit technology that has the capability of providing lower power-delay product than bipolar, nMOS, or GaAs technologies. CMOS technology is used for constructing integrated circuit (IC) chips, including microprocessors, microcontrollers, memory chips (including CMOS BIOS), and other digital logic circuits. CMOS technology is also used for analog circuits such as image sensors (CMOS sensors), data converters, RF circuits (RF CMOS), and highly integrated transceivers for many types of communication. CMOS overtook NMOS logic as the dominant MOSFET fabrication process for very large-scale integration (VLSI) chips in the 1980s, also replacing earlier transistor–transistor logic (TTL) technology. CMOS has since remained the standard fabrication process for MOSFET semiconductor devices in VLSI chips. CMOS fabrication can be carried out in many ways, which are discussed in detail below. 2. CMOS Fabrication Types: CMOS technology is used for implementing transistors due to low power dissipation. If we require a faster circuit then transistors are implemented over IC using BJT. Fabrication of CMOS transistors as IC’s can be done in three different methods. 1. N-well / P-well technology, where n-type diffusion is done over a p-type substrate or p-type diffusion is done over n-type substrate respectively. 2. The Twin well technology, where NMOS and PMOS transistor are developed over the wafer by simultaneous diffusion over an epitaxial growth base, rather than a substrate. 3. The silicon On Insulator process, where rather than using silicon as the substrate an insulator material is used to improve speed and latch-up susceptibility. 2.1 Twin Well Technology Using twin well technology, we can optimise NMOS and PMOS transistors separately. This means that transistor parameters such as threshold voltage, body effect and the channel transconductance of both types of transistors can be tuned independenly. n+ or p+ substrate, with a lightly doped epitaxial layer on top, forms the starting material for this technology. The n-well and pwell are formed on this epitaxial layer which forms the actual substrate. The dopant concentrations can be carefully optimized to produce the desired device characterisitcs because two independent doping steps are performed to create the well regions. The conventional n-well CMOS process suffers from, among other effects, the problem of unbalanced drain parasitics since the doping density of the well 2 region typically being about one order of magnitude higher than the substrate. This problem is absent in the twin-tub process. 2.2 Silicon on Insulator (SOI) To improve process characteristics such as speed and latch-up susceptibility, technologists have sought to use an insulating substrate instead of silicon as the substrate material. Completely isolated NMOS and PMOS transistors can be created virtually side by side on an insulating substrate (eg. sapphire) by using the SOI CMOS technology. This technology offers advantages in the form of higher integration density (because of the absence of well regions), complete avoidance of the latch-up problem, and lower parasitic capacitances compared to the conventional n-well or twin-tub CMOS processes. But this technology comes with the disadvantage of higher cost than the standard n-well CMOS process. Yet the improvements of device performance and the absence of latchup problems can justify its use, especially in deep submicron devices. 2.3 n-well & p-Well Processes 2.3.1 n-well Process The process steps involved in the n-well process are shown in Figure below. The process starts with a p-substrate. Step 1: A thin layer of SiO2 is deposited which will serve as a the pad oxide. Step 2: Deposition of a thicker sacrificial silicon nitride layer by chemical vapour deposition (CVD). Step 3: A plasma etching process using the complementary of the active area mask to create trenches used for insulating the devices. Step 4: The trenches are filled with SiO2 which is called as the field oxide. Step 5: To provide flat surface chemical mechanical planerization is performed and also sacrificial nitride is removed. Step 6: The n-well mask is used to expose only the n-well areas, after this implant and annealing sequence is applied to adjust the well doping. This is followed by second implant step to adjust the threshold voltage of the PMOS transistor. Step 7: Implant step is performed to adjust the threshold voltage of NMOS transistor. Step 8: A thin layer of gate oxide and polysilicon is chemically deposited and patterned with the help of polysilicon mask. Step 9: Ion implantation to dope the source and drain regions of the PMOS (p+) and NMOS (n+) transistors, this will also form n + polysilicon gate and p+ polysilicon gate for NMOS and PMOS transistors respectively. Hence this process is called as self aligned process. Step 10: Then the oxide or nitride spacers are formed by chemical vapour deposition. Step 11: In this step contact or via holes are etched, metal is deposited and patterned. After the deposition of last metal layer final passivation or overglass is deposited for protection. 3 Fig:1 – n-Well Process Steps 4 2.3.2 P-Well Process The CMOS fabrication steps of the p-well process are the same as that of an n-well process except that instead of an n-well a p-well is implanted. the process starts with an n-type substrate. Step 1: A thin Sio2 layer is deposited on an n-type semiconductor material which acts insulator to the environment. Step 2: Using chemical vapor deposition (CVD) the thick silicon nitride(si3No4) layer is deposited on the SIO2 layer. Step 3: A plasma etching process is used to make trenches for insulating the device from the external environment. Step 4: These trenches are filled with Sio2 which is called the field oxide which insulates the device. Step 5: Using the mechanical planarization process the sacrificial nitride layer and the pad oxide are removed until the flat surface is on the layer. Step 6: To adjust the doping process the p-well areas are exposed with masks and later annealing and implant are applied. This is followed by a second implant step to adjust the threshold voltage of the NMOS transistor. Step 7: The implant step is performed to adjust the threshold voltage of the PMOS transistor. Step 8: The metal contacts are made at the positions and the grounds are connected which prevents the device from high currents and voltages. Step 9: Ion implantation is carried out at the source and drain regions of PMOS (p+) and NMOS (n+) transistors, this will also form the n+ polysilicon gate and p+ polysilicon gate for NMOS and PMOS transistors respectively. This process is also known as the self-aligned method. Step 10: Oxide and Nitride spacers are formed by the chemical vapor deposition. Step 11: Holes are etched, metal is deposited, and patterned. After the deposition of the last metal layer final over-glass is deposited for protection. 5 Fig:2 – n-Well Process Steps 6 3. Advantages & Limitation of CMOS Technology: 3.1 Advantages of CMOS Technology 1. Low Power Consumption: One of the main advantages of CMOS technology is its low power consumption. In contrast to bipolar transistors, which consume a significant amount of power when in standby mode, CMOS transistors use almost no power when in off-state. This is because the current only flows through the device when it is in the on-state, which results in reduced power consumption and longer battery life in portable devices. 2. High Speed: CMOS technology has a higher switching speed than other technologies. This is because CMOS transistors operate in saturation mode, which allows them to switch rapidly between on and off states. This high-speed switching capability makes CMOS technology suitable for use in high-performance applications such as microprocessors and memory chips. 3. Small Size: CMOS technology allows the fabrication of transistors on a smaller scale. This enables the development of smaller and more compact devices. Additionally, the small size of CMOS devices also reduces manufacturing costs, which makes it an attractive option for mass production of devices. 4. Compatibility with Digital and Analog Circuits: CMOS technology is compatible with both digital and analog circuits. This means that it can be used in a wide range of applications, including data processing, signal processing, and power management. 5. High Efficiency: Electronic components manufactured using CMOS technology are highly efficient in operation. 6. Low Sensitivity: CMOS devices are less sensitive to high currents & voltage than devices fabricated using other methods. 3.2 Limitations of CMOS Technology 1. Sensitivity to Noise: CMOS technology is sensitive to noise and interference. The small size of the devices and the high-density layout makes it difficult to shield the circuit from external electromagnetic interference. This can result in reduced performance and even failure of the device. 2. Limited Voltage Tolerance: CMOS devices have a limited voltage tolerance. Exceeding the maximum voltage rating can result in permanent damage to the device. This is because the oxide layer in the transistor can be destroyed, which results in a permanent short circuit. 3. Design Complexity: CMOS technology is highly complex, and designing CMOS circuits can be challenging. The high level of complexity can result in higher development costs and longer development times. 4. Manufacturing Complexity: The manufacturing process for CMOS technology is highly complex and requires a clean and controlled environment. The high level of complexity also makes it difficult to ensure consistency in the manufacturing process, which can result in variations in the performance of the devices. 7 4. Conclusion: The CMOS Technology is currently a booming technology which had created a new era of electronic miniaturization and this evolution in electronic world is enhancing day by day. CMOS technology has claimed the predominant position in modern electronic systems. It has enabled the active use of microprocessors, communication systems and many others electronic devices with smaller sizes and higher efficiency rate. This growth is clearly seen through rapid fabrication of millions and billions transistor on single silicon chip. This report introduces the steps through which VLSI circuits are developed using the CMOS fabrication technology which provides relatively high-performance VLSI devices with low power consumption and small size. The fabrication techniques mentioned in this report are very efficient due to their characteristics and design simplicity. 8 5. References 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. Fundamentals of CMOS VLSI, By: V.S.Bagad, Edition 1, 2014 CMSO VLSI Design, Neil Weste, David Harris, 4th Edition, 2011 VLSI Design, By: K. Lal Kishore, V.S.V. Prabhakar,2009 https://electronics-club.com/cmos-fabrication-n-well-p-well-twin-tub-process/ https://www.geeksforgeeks.org/what-is-cmos-fabricationp-well-process/ https://medium.com/@agnathavasi360/cmos-fabrication-p-well-process-b40ee10ec132 https://www.electronics-tutorial.net/CMOS-Processing-Technology/n-well-Process/ https://www.electronics-tutorial.net/CMOS-Processing-Technology/p-well-Process/ https://www.vlsi4freshers.com/2020/03/cmos-fabrication-process.html https://www.ijsrp.org/research-paper-0417/ijsrp-p6430.pdf https://www.javatpoint.com/cmos-fabrication 9