FET Transistor

advertisement

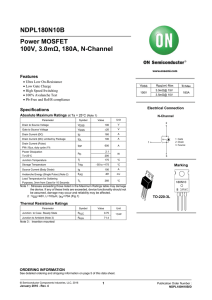

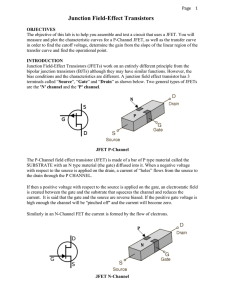

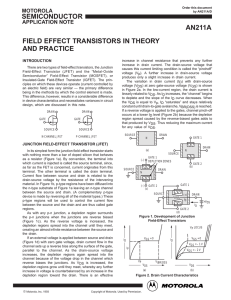

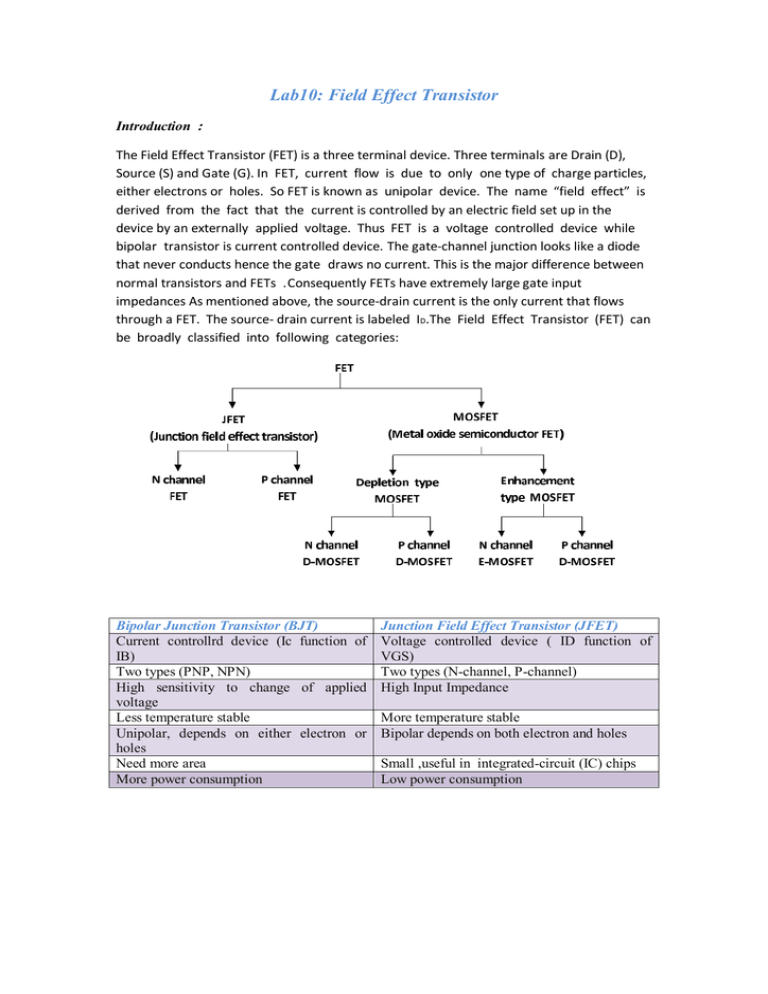

Lab10: Field Effect Transistor Introduction : The Field Effect Transistor (FET) is a three terminal device. Three terminals are Drain (D), Source (S) and Gate (G). In FET, current flow is due to only one type of charge particles, either electrons or holes. So FET is known as unipolar device. The name “field effect” is derived from the fact that the current is controlled by an electric field set up in the device by an externally applied voltage. Thus FET is a voltage controlled device while bipolar transistor is current controlled device. The gate-channel junction looks like a diode that never conducts hence the gate draws no current. This is the major difference between normal transistors and FETs .Consequently FETs have extremely large gate input impedances As mentioned above, the source-drain current is the only current that flows through a FET. The source- drain current is labeled ID.The Field Effect Transistor (FET) can be broadly classified into following categories: Bipolar Junction Transistor (BJT) Current controllrd device (Ic function of IB) Two types (PNP, NPN) High sensitivity to change of applied voltage Less temperature stable Unipolar, depends on either electron or holes Need more area More power consumption Junction Field Effect Transistor (JFET) Voltage controlled device ( ID function of VGS) Two types (N-channel, P-channel) High Input Impedance More temperature stable Bipolar depends on both electron and holes Small ,useful in integrated-circuit (IC) chips Low power consumption In this experiment we will obtain output characteristics of N-channel FET using CS ( Common source) Configuration. It is also known as drain characteristics. Basic construction of N-channel FET and its symbol are shown in the following figure. When gate to source voltage V GS is zero, N type channel is open so drain current will flow through it. As we increase negative voltage on the gate terminal,VGS=-1V, -2V, -3V etc., drain current reduces. The reduction in drain current is due to reduction in width of channel. As we increase negative gate voltage, width of depletion region spreads in the channel. Depletion region (generated field due to reverse bias ) does not have charge carriers so width of channel will reduce. As we increase negative value of VGS, penetration of depletion region (field) will be more and more due to which channel becomes narrower. At one point drain current reduces to zero when entire channel will be closed due to penetration of depletion region. The value of V GS at which drain current reduces to zero is called cut-off voltage VGS(off) Vp. Normally Drain current reduces to zero at VGS=-Vp. Thus VGS(off) = -VP where VP is pinch-off voltage . Pinch-off voltage VP is the value of voltage VDS at which drain current becomes constant (IDSS). IDSS is the maximum drain current for a JFET and is defined by the conditions VGS = 0 V and VDS >|VP|. The region to the right of the pinch-off locus of the above Fig is the region typically employed in linear amplifiers (amplifiers with minimum distortion of the applied signal) and is commonly referred to as the constant-current, saturation, or linear amplification region. Why the change in width of depletion region ? The reason for the change in width of the region is best described through the help of the below Fig. Assuming a uniform resistance in the n- channel, the re-sistance of the channel can be broken down to the divisions appearing in Fig. The current ID will establish the voltage levels through the channel as indicated on the same figure. The result is that the upper region of the p- type material will be reverse-biased by about 1.5 V, with the lower region only reverse-biased by 0.5 V. Recall from the discussion of the diode operation that the greater the applied reverse bias, the wider the depletion region —hence the distribution of the depletion region as shown in Fig. Check the N-Channel JFET: Testing a JFET with a multimeter might seem to be a relatively easy task, seeing as how it has only one PN junction to test: either measured between gate and source, or between gate and drain. Summary and useful formulas of the Field-Effect transistor: Gate-source junction must be reverse-bias . VGS controls ID . Value of V DS at which ID becomes zero is the cut off voltage VGS(OFF)=Vp I DSS is drain current when V GS = 0 . Transfer characteristic: Lab work Using Orcad plot the relation between Id and Vds at different values of Vgs And the relation between Id and Vgs for fixed value of Vds . Use (J2N3819) transistor from the JFET library