LAPORAN PRAKTIKUM 10

JFET

ELECTRONICS DEVICES

BONIFASIUS LEONARD A – 2201798276

TIRTA NATHANIEL WIJAYA – 2201765164

AUTOMOTIVE AND ROBOTIC ENGINEERING

BINUS-ASO SCHOOL OF ENGINEERING

Experiment 10

Junction Gate Field-Effect Transistor

I.

DASAR TEORI

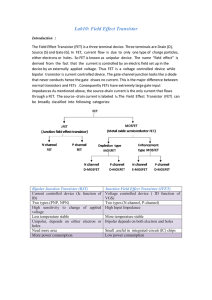

The junction gate field-effect transistor (JFET or JUGFET) is one of the simplest types of field-effect transistor. JFETs are three-terminal semiconductor devices that can be used as electronically-controlled switches, amplifiers, or voltage-controlled resistors.

JFETs can have an n-type or p-type channel. In the n-type, if the voltage applied to the gate is less than that applied to the source, the current will be reduced (similarly in the p-type, if the voltage applied to the gate is greater than that applied to the source). A JFET has a large input impedance (sometimes on the order of 10 10 ohms), which means that it has a negligible effect on external components or circuits connected to its gate.

The characteristics curves example shown above, shows the four different regions of operation for a JFET and these are given as:

Ohmic Region – When V

GS

= 0 the depletion layer of the channel is very small and the

JFET acts like a voltage controlled resistor.

Cut-off Region – This is also known as the pinch-off region were the Gate voltage,

V

GS

is sufficient to cause the JFET to act as an open circuit as the channel resistance is at maximum.

Saturation or Active Region – The JFET becomes a good conductor and is controlled by the Gate-Source voltage, ( V

GS

) while the Drain-Source voltage, ( V

DS

) has little or no effect.

Breakdown Region – The voltage between the Drain and the Source, ( V

DS

) is high enough to causes the JFET’s resistive channel to break down and pass uncontrolled maximum current.

The characteristics curves for a P-channel junction field effect transistor are the same as those above, except that the Drain current I

D

decreases with an increasing positive Gate-

Source voltage, V

GS

.

The Drain current is zero when V

GS

= V

P

. For normal operation, V

GS

is biased to be somewhere between V

P

and 0. Then we can calculate the Drain current, I

D

for any given bias point in the saturation or active region as follows:

Drain current in the active region.

Note that the value of the Drain current will be between zero (pinch-off) and I

DSS

(maximum current). By knowing the Drain current I

D

and the Drain-Source voltage V

DS

the resistance of the channel ( R

DS

) is given as:

Drain-Source Channel Resistance.

Where: g m

is the “transconductance gain” since the JFET is a voltage controlled device and which represents the rate of change of the Drain current with respect to the change in Gate-Source voltage.

Biasing of JFET Amplifier

II.

DATA

Tabel hasil multisim

V

DD

V

DS

I

V

GS

Volt

10

Volt

10

0 -0.4 -0.8 -1.2 -1.6 -2 -2.4 -2.8

2,951 1.737 0.844 0.269 14.156 0.011013 0.011013 0.011013

4 4 2.86 1.684 0.818 0.261 13.717 0.005063 0.005063 0.005063

3.2 3.2 2,848 1.677 0.814 0.26 13.658 0.004263 0.004263 0.004263

2.4 2.4 2,836 1.67 0.811 0.259 13.6 0.003419 0.003419 0.003419

1.6 1.6 2,792 1.663 0.807 0.258 13.541 0.00262 0.00262 0.00262

0.8 0.8 1,927 1.369 0.786 0.256 13.483 0.00181

0 0 0 0 0 0 0 0

0.00181

0

0.00181

0

Tabel hasil eksperiment

VDD

12

6.1

5.3

4.5

3.4

2.8

0

VDS

10

4

3.2

2.4

1.6

0.8

0

I

V

GS

(-0.4)

0.94mA

0.94mA

0.97mA

0.96mA

0.93mA

0.83mA

0

PRAKTEK

1,2

1

0,8

0,6

0,4

0,2

0

0 2 4 6 8 10 12

III.

ANALISA DATA

Pada data hasil simulasi dan praktikum, nilai kuat arus listrik memiliki perbedaan nilai dintara kedua data maupun nilai data yang terlalu kecil sehingga tidak dapat dibaca alat ukur bisa disebabkan karena keterbatasan alat ukur pada saat pratik.

IV.

REFERENSI

https://www.electronics-tutorials.ws/transistor/tran_5.html