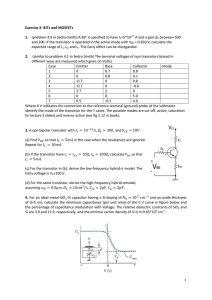

6. Field-Effect Transistor

advertisement

6. Field-Effect Transistor Outline: Introduction to three types of FET: JFET MOSFET & CMOS MESFET Constructions, Characteristics & Transfer curves of: JFET & MOSFET Field-Effect Transistor Introduction The field-effect transistor (FET) is a threeterminal device used for a variety of applications that match, to a large extent, those of the BJTs. The primary difference between the two types of transistor is the fact that: The BJT is a current-controlled device, whereas the FET is a voltage-controlled device. Field-Effect Transistor For BJT, the IC is a direct function of IB ; For FET, ID will be a function of the VGS . In both cases, output current is controlled by an input parameter. The term field effect: For the FET, an electric field is established by the charges present, which controls the conduction path of the output circuit without direct contact between the controlling and controlled quantities. Field-Effect Transistor The BJT is a bipolar device, which means that the conduction level is a function of two charge carriers, electrons & holes. The FET is a unipolar device, depending solely on either electrons or holes. One of the most important characteristics of the FET is its high input impedance. Typical Av of BJT is much greater than that of FET. Field-Effect Transistor FETs are more temperature stable than BJTs, and smaller than BJTs, making them particularly useful in integratedcircuit (IC) chips. Three types of FETs are presented here: Junction Field-Effect Transistor, JFET Metal Oxide Semiconductor Field-Effect Transistor, MOSFET Metal Semiconductor Field-Effect Transistor, MESFET Field-Effect Transistor For JFET: They are simply divided into n-channel and p-channel JFETs, of which the charge carries are electrons and holes respectively. For MOSFET: The category is further broken down into depletion and enhancement type, with each has n-channel and p-channel types. Field-Effect Transistor Due to its thermal stability & other general characteristics, MOSFET is widely used in computer & DSP fields. Furthermore, by using both n-channel and p-channel MOSFETs together, a new type of FET, Complementary MOSFET (CMOS) is created. It has high input impedance, fast switching speeds and low power consumption. Field-Effect Transistor CMOS logic design is now a new discipline. And modern digital logic devices, like DSP processors, micro-controllers and FPGAs, are all made of CMOS materials. For MESFET: It is a more recent development and takes full advantage of the high-speed property of GaAs for RF and computer design. However, it is relatively expensive. Field-Effect Transistor Figure: Difference between BJT & FET Field-Effect Transistor Construction of JFETs The JFET is a three-terminal device with one terminal capable of controlling the current between the other two. The n-channel device will be the prominent device, just like npn transistor in the discussion of BJT. For p-channel device, the result will be obtained by changing the signs of some parameters. Field-Effect Transistor The basic construction of n-channel JFET is shown in the figure. The major part of the structure is the ntype of material, which forms the channel between the embedded layer of p-type material. The top of the n-type of material is connected to a terminal called drain (D), whereas the lower end called source (S). Field-Effect Transistor The two p-type of material are connected together and to the gate (G) terminal. So the JFET has two p-n junctions under no-bias conditions. And a depletion region is generated at each junction with no free carrier. Also illustrated in the figure, it is the water analogy. Field-Effect Transistor The water pressure can be likened to the applied voltage from drain to source (inside the JFET), which establishes a flow of water (electrons) from the spigot (source). For FET, the gate through an applied potential, controls the flow of current to the drain. The terminology, (D, G & S), is defined for electron flow. Field-Effect Transistor Figure: JFET Construction Field-Effect Transistor Biasing: VGS = 0, VDS > 0 As shown in the figure, a positive voltage VDS ( =VDD)is applied across the channel. The gate is connected directly to the source to establish the condition VGS= 0. The electrons are drawn to the drain, leading to the current ID, which is also the same as IS. And the ID is solely limited by the resistance of the n-channel between D & S. Field-Effect Transistor The depletion region is wider near the top of both p-type materials. The reason is that upper region is more reverse-biased than the lower part, thus a wider depletion region. Also, the p-n junction is reverse-biased for the whole length of the channel, leading to no current in the gate terminal. IG = 0 is an important characteristic of JFET. Field-Effect Transistor When VDS increasing, ID will also increase. As VDS increases, the depletion regions will widen, causing reduction in the channel width and a higher resistance. If VDS is increased to a level VP, where it appear that the two depletion regions would touch, a condition referred to as pinch-off will result. Field-Effect Transistor The level of VDS that causes pinch-off condition is called pinch-off voltage, denoted by VP. Actually, under pinch-off condition, the current ID maintains a saturation level, defined as IDSS. IDSS is the maximum drain current for a JFET and is defined by the conditions VGS=0 and VDS > |VP|. Field-Effect Transistor Figure: Biasing of JFET (VGS = 0, VDS > 0) Field-Effect Transistor Figure: ID versus VDS for VGS = 0 Field-Effect Transistor Biasing: VGS < 0 For BJT, the characteristics is plotted to show the relationship between IC and VCE for different levels of IB. For FET, the characteristics is drawn to show the relationship between ID and VDS for various levels of VGS. The VGS is the controlling voltage of JFET, just like IB for the BJT. Field-Effect Transistor For the n-channel device, VGS is made more and more negative from its VGS = 0 level. The saturation level of ID has been reduced as VGS is made more and more negative. Eventually, when VGS = -VP , it is sufficiently negative to establish a saturation level that is zero. Field-Effect Transistor For all practical purpose, the device has been “turned off”. The VGS that results in ID = 0 is defined by VGS = VP , with VP being a negative voltage for n-channel and a positive voltage for pchannel JFETs. The region to the right of the pinch-off locus is employed in linear amplifier and referred to as linear amplification region. Field-Effect Transistor Figure: Biasing of JFET (VGS < 0) Field-Effect Transistor Figure: JFET characteristics (VGS < 0) Field-Effect Transistor Symbols of JFET The graphic symbols for the n-channel and p-channel JFETs are shown in the figure. Note that the arrow is pointing in for the nchannel device. This means that IG would flow if the p-n junction were forward-biased. For p-channel device, the only difference in the symbol is the direction of the arrow. Field-Effect Transistor Figure: Symbols of JFET Field-Effect Transistor Transfer Characteristics For BJT, the output current IC and input controlling current IB are related by constant , which is in the following equation form, IC= f(IB) = IB For JFET, the relationship between the output and input quantities is not as simple as the that of BJT. Field-Effect Transistor The relationship between the ID output and VGS is defined by Shockley’s equation: VGS I D I DSS 1 VP 2 where the IDSS and VP are constants, and VGS controls the ID. The squared term results in a nonlinear relationship between the ID output and VGS . Field-Effect Transistor The transfer characteristics are properties of JFET itself and are unaffected by the network in which the device is used. Obviously, the transfer characteristics can be obtained by Shockley’s equation. It can also be obtained from the output drain characteristics. We draw both curves with a common vertical scaling. Field-Effect Transistor One is a plot of ID versus VDS , whereas the other is ID versus VGS . Using the drain characteristics on the right of the vertical axis, we can draw a horizontal line from the saturation region of the curve to the ID axis. The result current level for both graphs is IDSS . Field-Effect Transistor The point of intersection on the ID versus VGS curve will be as shown since the vertical axis is defined as VGS = 0. If a horizontal line is drawn from the VGS = -1V curve to the ID axis and then extended to the other axis, another point on the transfer curve can be located. Continuing with VGS = -2V, -3V and VP (4V), we can complete the transfer curve. Field-Effect Transistor The transfer characteristics are a plot of an output current ID versus an inputcontrolling quantity, VGS . It’s a direct transfer from input to output variable. The non-linearity of the curve is obvious from the different space between curves of different VGS level, also from the curves themselves. It is the transfer curve of ID versus VGS that will receive extended use in the analysis of Chapter 7. Field-Effect Transistor Shorthand Method The transfer curves are useful and there are ways to plot it. By Shockley’s equation, it’s precise but the calculation is time-consuming. By the drain characteristics, it’s not easy since the drain characteristics should be known first. Here, a shorthand method will plot the curve in a efficient manner while maintaining an acceptable degree of accuracy. Field-Effect Transistor The basic concept of the shorthand method is that the curve is sketched out with only several key points which are easy to obtain. First, from Shockley’s equation VGS I D I DSS 1 VP If VGS = 0.5VP , then 2 2 VP / 2 0.25I DSS I D I DSS 1 VP Field-Effect Transistor If ID = 0.5IDSS , then VGS 0.5I DSS I DSS 1 VP So we get VGS 0.3VP . 2 If VGS = VP , then ID = 0. If VGS = 0, then ID = IDSS. So the transfer curve can be sketched to a satisfactory level of accuracy. Field-Effect Transistor Figure: Transfer curve by shorthand method Field-Effect Transistor p-channel JFET For p-channel devices, Shockley’s equation can still be applied exactly as it appears. In this case, both VGS and VP will be positive. The transfer characteristics will be the mirror image of the transfer curve obtained with an n-channel and the same limiting values. Field-Effect Transistor Figure: Transfer curve of p-channel JFET Field-Effect Transistor Summary of JFET Important equations of JFET are as following: VGS I D I DSS 1 VP ID = IS 2 IG 0 And the condition IG 0 is often the starting point for the analysis of a JFET configuration. Field-Effect Transistor MOSFET: Depletion-Type The basic construction of n-channel depletiontype MOSFET is shown in the figure. A slab of p-type material forms substrate. The S & D are connected through metallic contacts to n-doped regions linked by an nchannel. The G is also connected to a metal contact, but insulated from the n-channel by a silicon dioxide (SiO2) layer. Field-Effect Transistor It is this layer of SiO2 that accounts for IG = 0 and the desirable high input impedance of the device. Some devices provide an additional terminal labeled SS. But in most cases, the substrate and source are connected. From the above, the reason for the name of Metal Oxide Semiconductor FET is clear. Field-Effect Transistor Figure: n-Channel depletion-type MOSFET Field-Effect Transistor Transfer Characteristics Shown in the figure, it is the configuration of n-channel depletion-type MOSFET. The substrate and source are connected as a three-terminal device. A positive potential is applied to VDS. An adjustable potential is applied to VGS. When VGS < 0, the transfer curve is like that of n-channel JFET. Field-Effect Transistor When VGS > 0, the drain current ID will increase at a rapid rate. So the positive VGS has “enhanced” the level of ID and leads to the enhancement region. The region to the left of the vertical axis is the depletion region. The Shockley’s equation is still be applicable for the depletion-type MOSFET. Field-Effect Transistor Figure: Configuration of n-channel depletion-type MOSFET Field-Effect Transistor For the plot of the transfer characteristics of an n-channel depletion-type MOSFET by shorthand method, please see Example 6.3. Shown in the figure, it’s the transfer curve of the p-channel depletion-type MOSFET. It is exactly the opposite of that of n-channel. The VGS is positive for most of time and can also be negative. And when VGS = 0, ID = IDSS . Field-Effect Transistor Symbols of Depletion-Type MOSFET The graphic symbols for the n-channel and p-channel depletion-type MOSFET are shown in the figure. The D & S is connected by channel through the vertical line in the symbol. The lack of a direct connection between G and channel is shown. The substrate is connected internally as a 3terminal device. Field-Effect Transistor Figure: Symbols of depletion-type MOSFET Field-Effect Transistor MOSFET: Enhancement-Type Shown in the figure is the basic construction of n-channel enhancement-type MOSFET. A slab of p-type material forms substrate. The S & D are connected through metallic contacts to n-doped regions . The silicon dioxide (SiO2) layer is still present to isolate the gate platform from the region between D & S. Field-Effect Transistor Note the absence of a channel between the two n-doped regions. This is the primary difference between the construction of depletion-type and enhancement-type MOSFETs. The characteristics of the enhancementtype MOSFET are quite different from anything obtained thus far. The transfer curve is NOT defined by Shockley’s equation. Field-Effect Transistor Figure: n-Channel enhancement-type MOSFET Field-Effect Transistor Transfer Characteristics Shown in the figure, it is the configuration of n-channel enhancement-type MOSFET. The substrate and source are connected as a three-terminal device. A positive potential is applied to VDS. When VGS = 0, the absence of an n-channel will result in a zero current. Field-Effect Transistor As VGS increases in magnitude, an induced n-type region is formed near the SiO2 layer. This leads to a measurable current flow between D & S. The level of VGS that results in the significant increase in drain current ID is called the threshold voltage, VT . The channel is enhanced by VGS > 0. This is the reason to the name of this type of MOSFET. Field-Effect Transistor If we hold VGS constant and increase VDS , the ID will eventually reach a saturation level. This is the result of the narrower channel at the drain end of the induced channel. The drain characteristics is shown in the figure. For a fixed value of VT, the higher level of VGS , the greater is the saturation level for VDS. Field-Effect Transistor For VGS less than VT , ID = 0. It is noticeable that the spacing between the level of VGS increases as the magnitude of VGS increases. This shows the nonlinear relationship between ID and VGS . Actually, ID = k (VGS – VT)2 where k is a constant and can be obtained through VGS(on) and ID(on) from datasheet. Field-Effect Transistor Furthermore, transfer curve can be obtained by setting it side by side with drain characteristics. If a horizontal line is drawn from the VGS = +8V curve to the ID axis and then extended to the other axis, a point on the transfer curve can be located. Continuing with other voltages of VGS , the transfer curve is obtained. Field-Effect Transistor It must be remembered that ID is zero for VGS VT. Also, the transfer curve is totally in the positive VGS region and does not rise until VGS = VT. As to how to plot the transfer curve given k and VT for a particular MOSFET, see Figure 6.37 on page 330. Field-Effect Transistor Figure: Channel formation in the n-channel enhancement-type MOSFET Field-Effect Transistor Figure: Drain & transfer characteristics for n-channel enhancement-type MOSFET Field-Effect Transistor p-Channel Enhancement-Type MOSFET The construction of p-channel enhancementtype MOSFET is exactly the reverse of that of n-channel one. A slab of n-type material forms substrate. Those p-doped regions are under the drain and source connections. All the voltage polarities and current directions are reversed. Field-Effect Transistor The drain characteristics of p-channel enhancement-type MOSFET is shown in the figure. The ID is increasing from increasingly negative values of VGS. Also, ID is zero while |VGS| < VT. The equation of ID discussed before is also applicable to p-channel devices. Field-Effect Transistor Symbols of Enhancement-Type MOSFET The graphic symbols for the n-channel and p-channel enhancement-type MOSFET are shown in the figure. The dashed line between D & S reflects that a channel does not exist. The direction of arrow shows the channel type of the device. The substrate is connected internally as a 3terminal device. Field-Effect Transistor Figure: Symbols of enhancement-type MOSFET Field-Effect Transistor Summary of Chapter 6 Introduction to FET For JFET & MOSFET Output characteristics: ID~VDS Transfer curves: ID~VGS Shorthand method to sketch transfer curves Graphical symbols Field-Effect Transistor