Review of BJTs, JFETs and MOSFETs

advertisement

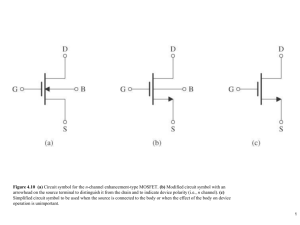

EE-4232 Review of BJTs, JFETs and MOSFETs 0 A simplified structure of the npn transistor. 1 A simplified structure of the pnp transistor. 2 Current flow in an npn transistor biased to operate in the active mode, (Reverse current components due to drift of thermally generated minority carriers are not shown.) 3 Current flow in an pnp transistor biased to operate in the active mode. 4 The iC-vCB characteristics for an npn transistor in the active mode. 5 (a) Conceptual circuit for measuring the iC-vCE characteristics of the BJT. (b) The iC-vCE characteristics of a practical BJT. 6 (a) Conceptual circuit to illustrate the operation of the transistor of an amplifier. (b) The circuit of (a) with the signal source vbe eliminated for dc (bias) analysis. 7 Linear operation of the transistor under the small-signal condition: A small signal vbe with a triangular waveform is superimpose din the dc voltage VBE. It gives rise to a collector signal current ic, also of triangular waveform, superimposed on the dc current IC. Ic = gm vbe, where gm is the slope of the ic - vBE curve at the bias point Q. 8 Two slightly different versions of the simplified hybrid-Π model for the small-signal operation of the BJT. The equivalent circuit in (a) represents the BJT as a voltagecontrolled current source ( a transconductance amplifier) and that in (b) represents the BJT as a current-controlled current source (a current amplifier). 9 Two slightly different versions of what is known as the T model of the BJT. The circuit in (a) is a voltage-controlled current source representation and that in (b) is a currentcontrolled current source representation. These models explicitly show the emitter resistance re rather than the base resistance rΠ featured in the hybrid-π model. 10 Junction Field-Effect Transistors iD n-JFET vGS =0 IDSS vGS =-1 Pinch-off vDG > -Vp vGS =Vp -Vp iD vDS p-JFET vSG =0 IDSS vSG =-1 Pinch-off vGD > Vp vSG =-Vp Vp vSD Junction Field-Effect Transistors Triod (VCR) Region i D = I DSS r DS v DS = -------iD v GS v DS v DS 2 2 1 – -------- ---------- – ------- V p – V p V p v DS = small 2I DSS v GS = -------------- 1 – -------–V p Vp Boundary v DG = – V p iD v DS = I DSS ------- Vp 2 Pinch-Off Region iD v GS 2 = I DSS 1 – ------- Vp –1 MOSFETs 11 Physical structure of the enhancement-type NMOS transistor: (a) perspective view; (b) cross section. Typically L = 1 to 10 µm, W = 2 to 500 µm, and the thickness of the oxide layer is in the range of 0.02 to 0.1 µm. 12 The enhancement-type NMOS transistor with a positive voltage applied to the gate. An n channel is induced at the top of the substrate beneath the gate. 13 The drain current iD versus the drain-to-source voltage vDS for an enhancement-type NMOS transistor operated with vGS > Vt. 14 Cross section of a CMOS integrated circuit. Note that the PMOS transistor is formed in a separate n-type region, known as an n well. Another arrangement is also possible in which an n-type body is used and the n device is formed in a p well. 15 (a) An n-channel enhancement-type MOSFET with vGS and vDS applied and with the normal directions of current flow indicated. (b) The iD - vDS characteristics for a device with Vt = 1 V and k’n(W/L) = 0.5 mA/V2. 16 The iD - vGS characteristic for an enhancement-type NMOS transistor in saturation (Vt = 1 V and k’n(W/L) = 0.5 mA/V2). 17 Large-signal equivalent circuit model of the n-channel MOSFET in saturation, incorporating the output resistance ro. The output resistance models the linear dependence of iD on vDS and is given by ro ≅ VA/ID. 18 Conceptual circuit utilized to study the operation of the MOSFET as an amplifier. 19 Small-signal operation of the enhancement MOSFET amplifier. 20 Small-signal models for the MOSFET: (a) neglecting the dependence of iD on vDS in saturation (channel-length modulation effect); and (b) including the effect of channellength modulation modeled by output resistance ro = |VA|/ID. 21 (a) The CMOS inverter. (b) Simplified circuit schematic for the inverter. 22 Dynamic operation of a capacitively loaded CMOS inverter: (a) circuit; (b) input and output waveforms. 23