solution to Assignment 3

advertisement

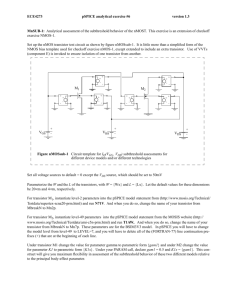

HW#3 Solution Dr. Parker Fall 2014 Assume for the problems below that Vdd = 1.8 V, Vtp0 is -.7 V. and Vtn0 is .7 V. Vtpbodyeffect is -.9 V. and Vtnbodyeffect is .9 V. lambda=100 nm. Assume ßn (kn)= 219.4 W/L µ A(microamps)/V2 and ßp (kp)= 51 W/L µ A/V2 1. (10%) A PMOS transistor has Vs = 1.7 V , Vd = .9 V. Vgd = -.3 V. What region of operation is it in? Vgd= -.3; Vgd= Vg- Vd=> Vg = Vgd + Vd = -.3 V + .9 V=.6 V Vtpbodyeffect= -.9 V (there is body effect since the source is not tied to the lowest potential) Vds=.9-1.7= -.8 V Vgs=.6-1.7= -1.1 V Is the transistor ON? Vgs ≤ Vtpbodyffect? -1.1 ≤ -.9 ? True, so transistor is ON Vds > Vgs-Vtp? -.8 > -1.1 – (-.9)? -.8 > -.2? False, transistor is in SATURATION region 2. (10 %) An NMOS transistor has Vds = 1.2 V. Vd = 1.3 V. Is the transistor in the saturation region of operation when Vgs =1.1 V? Vds =Vd-Vs 1.2 = 1.3 – Vs Vs=1.3 -1.2 =.1 V There is body effect since the source of the transistor is not connected to the lowest potential. Vgs ≥Vtpbodyffect? 1.1 ≥ .9? True, transistor is ON Vds> Vgs –Vtnbodyeffect? 1.2 > 1.1 - .9? 1.2 > .2? The transistor is in SATURATION region 3. a) (5 %) A PMOS transistor is used as a pass transistor (switch). The input voltage is Vin = 1.6 V. The gate voltage Vgs=-1 V. The voltage Vout = .7 V at time t = 0+. What is the final output voltage at t = infinity? The source is at the input, so if it is ON the it doesn’t limit the output voltage. To verify if the transistor is ON, we test for Vgs ≤ Vtpbodyffect; Vgs = -1 V, Vtpbodyeffect = -.9V, so the the above inequality is true and therefore the transistor is ON. Therefore, the output at t=infinity is 1.6V. b) (3%) Does the PMOS transistor have body effect when t approaches infinity? Yes, it does have body effect because the source terminal is different from the highest potential. c) (10%) Assume the transistor width is three times unit size and the length is twice minimum size. Compute the drain current flow IDS at t = 0+ and at t=infinity. At t=0+, Vds= .7-1.6= -.9 V Vgs= -1 V Vtpbodyeffect= -.9 V (the source is lower than the highest potential) Vgs ≤ Vtpbodyeffect? If this condition is true, the transistor is ON. -1 ≤ -.9? The condition is true, so the transistor is ON. Vds > Vgs-Vtpbodyeffect? -.9 > -1 – (-.9)? -.9 > -1? False, so the transistor is in SATURATION region Idsp = .5*µp*Cox*W/L*(Vgs-Vtpbodyeffect)^2 =.5*(51x10^-6)((3*(4*lambda))/(2*(2*lambda))(-1- (-.9))^2 = -.765 uA (negative sign indicates the current flow direction) At t=infinity Vds= 0 V Vgs= -1 V Vtpbodyeffect= -.9 V Vgs ≤ Vtpbodyeffect? If this condition is true, the transistor is ON -1 ≤ -.9? The condition is true, so the transistor is ON. Vds > Vgs-Vtpbodyeffect? If the condition is true the transistor is in linear region 0 > -1 – (-.9)? 0 > -.1 ? True, so the transistor is in LINEAR region Idsp = µp*Cox*W/L*Vds*(Vgs-Vtpbodyeffect – Vds/2) Idsp= 0 A 4. a) (7 %) Identify the sources and drains in a transmission gate at t=0+ when Vin = .6 V and Vout = 1.3 V. Vgn = 1.6 V, and Vgp = .2 V. b) (8 %) What regions are the two transistors in when t approaches infinity? Be sure to justify your answers. NMOS: We have body effect because the source terminal of the nmos is not connected to the lowest potential. First, let’s investigate if the transistor is ON: Vgs= 1.6 -.6 = 1 V Vgs ≥Vtpbodyffect? 1V ≥ .9 ? True, so the transistor is ON Since the NMOS transistor is ON, and the source is not at the output, then the NMOS pass transistor can pass the input voltage and at t= infinity the output voltage is .6 V Vgs= 1 V Vds= .6 - .6 =0 V Vds < Vgs-Vtnbodyeffect? bodyeffect? If this condition is true, then the transistor is in linear region. 0 < 1 -.9? True, the NMOS transistor is in LINEAR region PMOS: Vgs = .2 -.6 = -.4 V Vgs ≤ Vtpbodyeffect? -.4 V ≤ -.9 V? False, the PMOS transistor is in cut-off 5. a) (10%) In the circuit below, what are the voltages at node A and Out at t=infinity? For the NMOS transistor, ansistor, the drain is at node A and the source is at VIn.. For the PMOS, the source is at node Out and the drain is at node A A. If the NMOS transistor is ON, node A at t=infinity is equal to VIn. NMOS: Let’s investigate if the transistor is ON: Vgs= 1.8 -.5 = 1.3 V Vgs ≥Vtpbodyffect? 1.3 ≥ .9 ? True, so transistor is ON At t=infinity the voltage at node A is Vin, so node A is equal to .5 V PMOS: Node Out is the source terminal. We have body effect since the source at t=infinity the source is not the highest potential. For the transistor to be ON: Vgs ≤ Vtpbodyeffect From this above inequality we get that, Vg - Vs ≤ Vtpbodyeffect Vs ≥ Vg – Vtpbodyeffect Vs ≥ 0 – (-.9); Vs ≥ .9; therefore at =infinity the output voltage Out=.9 V b) (5%) If the input Vin cannot be transfered to the output, what would be the range of voltages that you could apply to the gate of the pmos transistor to transfer Vin. Assume you can use a negative power supply. Any voltage less than or equal to VIn – Vtpbodyeffect, so Vg ≤ -.4 is good. The pmos transistor is ON when the source terminal is greater than the gate terminal by the threshold of the transistor; so as long as the gate voltage is low enough to satisfy this condition, the pmos transistor is able to transfer the voltage at node A. 6. (5%) What is the effective channel resistance of a PMOS transistor of 10 lambda width and minimum length? Assume Vgs=-1.7 V, Vds= -.5V, Vg=0. Let’s first verify that the transistor is ON and in LINEAR region Vgs = -1.7 V Vgs = Vg – Vs Vs = Vg –Vgs = 1.7 V (we have body effect) Vgs ≤ Vtpbodyeffect ? True, therefore the transistor is ON. Vds = -.5 V Vds> Vgs – Vtpbodyeffect ? -.5 > -1.7 – (-.9)? -.5 > -.8? This is true, so the PMOS transistor is in LINEAR region. Rchp = 1/( ßp*W/L*(Vgs-Vtpbodyeffect)) Rchp = |1/(51X10^-6*((10*lambda)/(2*lambda))*(-1.7-(-.9))| Rchp = 4.9 KΩ 7. (5%) What type of parasitic transistors causes latchup? Briefly explain how latchup can occur. Parasitic bipolar transistors causes latchup. Latchup occurs when we have current flowing between Vdd and ground away from the transistor channels in a CMOS process 8. (5%) Assume a channel is formed between drain and source of an NMOS transistor, so that the transistor is in linear region. If we continuously increase slowly the drain voltage, what would happen to the channel eventually? Would the transistor still be in linear region? If we increase the drain of the transistor we pull electrons from the pool of the n+diffusion, reducing the depth of the channel at the drain side. At some point, when the drain is high enough to meet the condition Vds=Vgs-Vthreshold, the channel is said to be in pinched-off region (the border between linear and saturation). If we keep increasing Vd, the transistor will move to saturation region. 9. (5%) Why do we need to have some space between the p+ diffusions to the edge of the n-well? We need to have some space between the p+ diffusions to the edge of the n-well to avoid a short circuit with the p-substrate 10. (7%) What is electromigration? How can it be avoided? Electromigration is the process through which a metal can break resulting in an open circuit due to the increase of the current density. For example, if a particle falls into a metal, so that the metal width is reduced, this makes a narrow tunnel through which current can flow faster. As a result as the electrons are flowing they start picking up metal atoms and moving them until finally the metal breaks causing an open circuit. It can be avoided by design rules, the minimum width in for metal is 3*lambda 11. (5%) What is the minimum distance in micrometers allowed between two unconnected metal1 features to prevent design rule violations? 3*lambda= .3 micrometers