Lecture 21 REMINDERS

advertisement

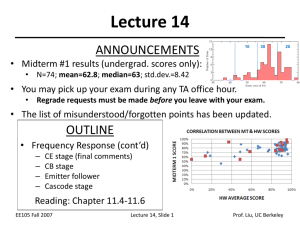

Lecture 21 REMINDERS • Review session: Fri. 11/9, 3-5PM in 306 Soda (HP Auditorium) • Midterm #2 (Thursday 11/15, 3:30-5PM in Sibley Auditorium) OUTLINE • Frequency Response – – – – – – Review of basic concepts high-frequency MOSFET model CS stage CG stage Source follower Cascode stage Reading: Chapter 11 EE105 Fall 2007 Lecture 21, Slide 1 Prof. Liu, UC Berkeley Av Roll-Off due to CL • The impedance of CL decreases at high frequencies, so that it shunts some of the output current to ground. 1 0 p RD C L 1 Av g m RD || jCL • In general, if node j in the signal path has a smallsignal resistance of Rj to ground and a capacitance Cj to ground, then it contributes a pole at frequency (RjCj)-1 EE105 Fall 2007 Lecture 21, Slide 2 Prof. Liu, UC Berkeley Pole Identification Example 1 0 p1 EE105 Fall 2007 1 RG Cin p2 Lecture 21, Slide 3 1 RD C L Prof. Liu, UC Berkeley Pole Identification Example 2 0 p1 1 1 RG || Cin gm EE105 Fall 2007 p2 Lecture 21, Slide 4 1 RD C L Prof. Liu, UC Berkeley Dealing with a Floating Capacitance • Recall that a pole is computed by finding the resistance and capacitance between a node and (AC) GROUND. • It is not straightforward to compute the pole due to CF in the circuit below, because neither of its terminals is grounded. EE105 Fall 2007 Lecture 21, Slide 5 Prof. Liu, UC Berkeley Miller’s Theorem • If Av is the voltage gain from node 1 to 2, then a floating impedance ZF can be converted to two grounded impedances Z1 and Z2: V1 V2 V1 V1 1 Z1 Z F ZF ZF Z1 V1 V2 1 Av V1 V2 V2 V2 1 Z 2 Z F ZF ZF Z2 V1 V2 1 1 EE105 Fall 2007 Lecture 21, Slide 6 Av Prof. Liu, UC Berkeley Miller Multiplication • Applying Miller’s theorem, we can convert a floating capacitance between the input and output nodes of an amplifier into two grounded capacitances. • The capacitance at the input node is larger than the original floating capacitance. ZF Z2 1 1 1 1 jCF 1 1 j 1 1 CF Av Av Av 1 ZF 1 jC F Z1 1 Av 1 Av j 1 Av C F EE105 Fall 2007 Lecture 21, Slide 7 Prof. Liu, UC Berkeley Application of Miller’s Theorem 0 1 in RG 1 g m RD C F EE105 Fall 2007 out Lecture 21, Slide 8 1 1 C F RD 1 g m RD Prof. Liu, UC Berkeley MOSFET Intrinsic Capacitances The MOSFET has intrinsic capacitances which affect its performance at high frequencies: 1. gate oxide capacitance between the gate and channel, 2. overlap and fringing capacitances between the gate and the source/drain regions, and 3. source-bulk & drain-bulk junction capacitances (CSB & CDB). EE105 Fall 2007 Lecture 21, Slide 9 Prof. Liu, UC Berkeley High-Frequency MOSFET Model • The gate oxide capacitance can be decomposed into a capacitance between the gate and the source (C1) and a capacitance between the gate and the drain (C2). – In saturation, C1 (2/3)×Cgate, and C2 0. – C1 in parallel with the source overlap/fringing capacitance CGS – C2 in parallel with the drain overlap/fringing capacitance CGD EE105 Fall 2007 Lecture 21, Slide 10 Prof. Liu, UC Berkeley Example CS stage EE105 Fall 2007 …with MOSFET capacitances explicitly shown Lecture 21, Slide 11 Simplified circuit for high-frequency analysis Prof. Liu, UC Berkeley Transit Frequency • The “transit” or “cut-off” frequency, fT, is a measure of the intrinsic speed of a transistor, and is defined as the frequency where the current gain falls to 1. Conceptual set-up to measure fT I out g mVin I in Vin Z in 1 I out 1 g m Z in g m I in jT Cin g T m Cin gm 2f T CGS EE105 Fall 2007 Lecture 21, Slide 12 Prof. Liu, UC Berkeley Small-Signal Model for CS Stage 0 EE105 Fall 2007 Lecture 21, Slide 13 Prof. Liu, UC Berkeley … Applying Miller’s Theorem p ,in 1 RThev Cin 1 g m RD CGD p ,out 1 1 CGD RD Cout 1 g R m D Note that p,out > p,in EE105 Fall 2007 Lecture 21, Slide 14 Prof. Liu, UC Berkeley Direct Analysis of CS Stage • Direct analysis yields slightly different pole locations and an extra zero: gm z C XY 1 p1 1 g mRD C XY RThev RThevCin RD C XY Cout 1 g m RD C XY RThev RThev Cin RD C XY Cout p2 RThev RD CinC XY CoutC XY CinCout EE105 Fall 2007 Lecture 21, Slide 15 Prof. Liu, UC Berkeley I/O Impedances of CS Stage 0 Z in j CGS EE105 Fall 2007 1 1 g m RD CGD Z out Lecture 21, Slide 16 1 j CGD C DB || RD Prof. Liu, UC Berkeley CG Stage: Pole Frequencies CG stage with MOSFET capacitances shown p, X 0 1 1 RS || C X gm C X CGS CSB p ,Y 1 RD CY CY CGD CDB EE105 Fall 2007 Lecture 21, Slide 17 Prof. Liu, UC Berkeley AC Analysis of Source Follower 0 vout vin CGS 1 j gm 2 a j b j 1 EE105 Fall 2007 • The transfer function of a source follower can be obtained by direct AC analysis, similarly as for the emitter follower (ref. Lecture 14, Slide 6) RS CGDCGS CGDC SB CGS C SB a gm b RS CGD Lecture 21, Slide 18 CGD C SB gm Prof. Liu, UC Berkeley Example vout vin CGS 1 j gm 2 a j b j 1 RS CGD1CGS1 (CGD1 CGS1 )(CSB1 CGD 2 CDB 2 ) a g m1 CGD1 C SB1 C GD 2 C DB 2 b RS CGD1 g m1 EE105 Fall 2007 Lecture 21, Slide 19 Prof. Liu, UC Berkeley Source Follower: Input Capacitance • Recall that the voltage gain of a source follower is Av Follower stage with MOSFET capacitances shown 0 RS 1 RS gm • CXY can be decomposed into CX and CY at the input and output nodes, respectively: C X 1 Av CGS CGS 1 g m RS CGS Cin CGD 1 g m RS EE105 Fall 2007 Lecture 21, Slide 20 Prof. Liu, UC Berkeley Example 0 1 Cin CGD1 CGS1 1 g m1 rO1 || rO 2 EE105 Fall 2007 Lecture 21, Slide 21 Prof. Liu, UC Berkeley Source Follower: Output Impedance 0 • The output impedance of a source follower can be obtained by direct AC analysis, similarly as for the emitter follower (ref. Lecture 14, Slide 9) jRG CGS 1 vX iX jCGS g m EE105 Fall 2007 Lecture 21, Slide 22 Prof. Liu, UC Berkeley Source Follower as Active Inductor Z out jRG CGS 1 jCGS g m CASE 1: RG < 1/gm CASE 2: RG > 1/gm • A follower is typically used to lower the driving impedance, i.e. RG is large compared to 1/gm, so that the “active inductor” characteristic on the right is usually observed. EE105 Fall 2007 Lecture 21, Slide 23 Prof. Liu, UC Berkeley Example 3 0 Z out EE105 Fall 2007 j rO1 || rO 2 CGS 3 1 jCGS 3 g m 3 Lecture 21, Slide 24 Prof. Liu, UC Berkeley MOS Cascode Stage • For a cascode stage, Miller multiplication is smaller than in the CS stage. Av , XY 1 vX 1 g m1 vY gm2 CX 2CXY EE105 Fall 2007 Lecture 21, Slide 25 Prof. Liu, UC Berkeley Cascode Stage: Pole Frequencies 0 Cascode stage with MOSFET capacitances shown (Miller approximation applied) p ,out p ,Y p, X 1 g RG CGS1 1 m1 gm2 EE105 Fall 2007 CGD1 1 RD C DB 2 CGD 2 1 1 gm2 gm2 C C 1 DB1 GS 2 g m1 Lecture 21, Slide 26 CGD1 C SB 2 Prof. Liu, UC Berkeley Cascode Stage: I/O Impedances 0 Z in 1 g m1 CGD1 j CGS1 1 gm2 EE105 Fall 2007 Z out RD || Lecture 21, Slide 27 1 j CGD 2 C DB 2 Prof. Liu, UC Berkeley