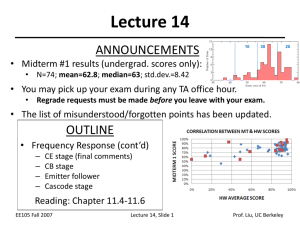

Lecture 13 ANNOUNCEMENTS • Midterm #1 (Thursday 10/11, 3:30PM-5:00PM) location:

advertisement

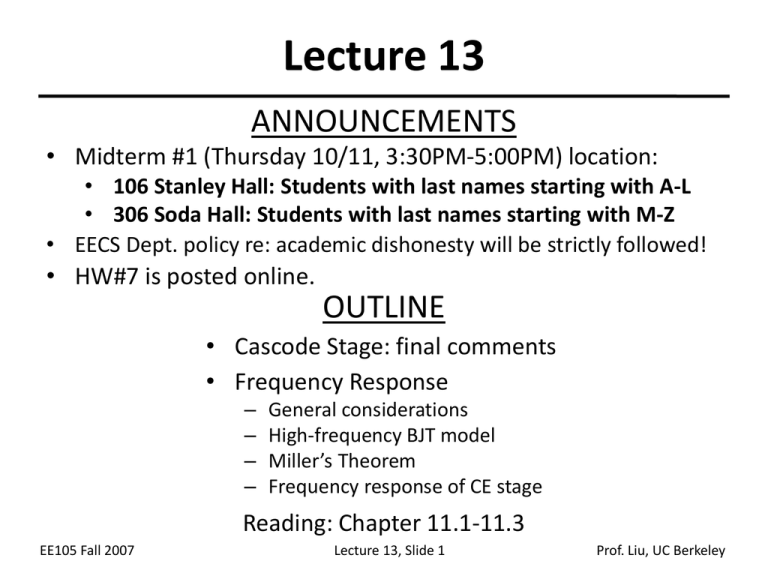

Lecture 13 ANNOUNCEMENTS • Midterm #1 (Thursday 10/11, 3:30PM-5:00PM) location: • 106 Stanley Hall: Students with last names starting with A-L • 306 Soda Hall: Students with last names starting with M-Z • EECS Dept. policy re: academic dishonesty will be strictly followed! • HW#7 is posted online. OUTLINE • Cascode Stage: final comments • Frequency Response – – – – General considerations High-frequency BJT model Miller’s Theorem Frequency response of CE stage Reading: Chapter 11.1-11.3 EE105 Fall 2007 Lecture 13, Slide 1 Prof. Liu, UC Berkeley Cascoding Cascode? • Recall that the output impedance seen looking into the collector of a BJT can be boosted by as much as a factor of b, by using a BJT for emitter degeneration. Rout [1 g m1 (ro 2 || r 1 )]ro1 ro 2 || r 1 Rout g m1ro1 ro 2 || r 1 bro1 • If an extra BJT is used in the cascode configuration, the maximum output impedance remains bro1. Rout [1 g m1 ( bro 2 || r 1 )]ro1 bro 2 || r 1 Rout,max g m1ro1r 1 bro1 EE105 Fall 2007 Lecture 13, Slide 2 Prof. Liu, UC Berkeley Cascode Amplifier • Recall that voltage gain of a cascode amplifier is high, because Rout is high. Av g m1ro1 g m2 ro1 r 2 • If the input is applied to the base of Q2 rather than the base of Q1, however, the voltage gain is not as high. – The resulting circuit is a CE amplifier with emitter degeneration, which has lower Gm. io gm2 Gm vin 1 g m 2 ro1 ro 2 EE105 Fall 2007 Lecture 13, Slide 3 Prof. Liu, UC Berkeley Review: Sinusoidal Analysis • Any voltage or current in a linear circuit with a sinusoidal source is a sinusoid of the same frequency (w). – We only need to keep track of the amplitude and phase, when determining the response of a linear circuit to a sinusoidal source. • Any time-varying signal can be expressed as a sum of sinusoids of various frequencies (and phases). Applying the principle of superposition: – The current or voltage response in a linear circuit due to a time-varying input signal can be calculated as the sum of the sinusoidal responses for each sinusoidal component of the input signal. EE105 Fall 2007 Lecture 13, Slide 4 Prof. Liu, UC Berkeley High Frequency “Roll-Off” in Av • Typically, an amplifier is designed to work over a limited range of frequencies. – At “high” frequencies, the gain of an amplifier decreases. EE105 Fall 2007 Lecture 13, Slide 5 Prof. Liu, UC Berkeley Av Roll-Off due to CL • A capacitive load (CL) causes the gain to decrease at high frequencies. – The impedance of CL decreases at high frequencies, so that it shunts some of the output current to ground. 1 Av g m RC || jwCL EE105 Fall 2007 Lecture 13, Slide 6 Prof. Liu, UC Berkeley Frequency Response of the CE Stage • At low frequency, the capacitor is effectively an open circuit, and Av vs. w is flat. At high frequencies, the impedance of the capacitor decreases and hence the gain decreases. The “breakpoint” frequency is 1/(RCCL). Av EE105 Fall 2007 Lecture 13, Slide 7 g m RC R C w 1 2 C 2 L 2 Prof. Liu, UC Berkeley Amplifier Figure of Merit (FOM) • The gain-bandwidth product is commonly used to benchmark amplifiers. – We wish to maximize both the gain and the bandwidth. • Power consumption is also an important attribute. – We wish to minimize the power consumption. 1 g m RC RC C L Gain Bandwidth Power Consumptio n I CVCC 1 VT VCC C L Operation at low T, low VCC, and with small CL superior FOM EE105 Fall 2007 Lecture 13, Slide 8 Prof. Liu, UC Berkeley Bode Plot • The transfer function of a circuit can be written in the general form jw jw 1 1 A is the low-frequency gain 0 w z1 w z 2 wzj are “zero” frequencies H ( jw ) A0 wpj are “pole” frequencies j w j w 1 1 w w p1 p2 • Rules for generating a Bode magnitude vs. frequency plot: – As w passes each zero frequency, the slope of |H(jw)| increases by 20dB/dec. – As w passes each pole frequency, the slope of |H(jw)| decreases by 20dB/dec. EE105 Fall 2007 Lecture 13, Slide 9 Prof. Liu, UC Berkeley Bode Plot Example • This circuit has only one pole at ωp1=1/(RCCL); the slope of |Av|decreases from 0 to -20dB/dec at ωp1. 1 w p1 RC C L • In general, if node j in the signal path has a smallsignal resistance of Rj to ground and a capacitance Cj to ground, then it contributes a pole at frequency (RjCj)-1 EE105 Fall 2007 Lecture 13, Slide 10 Prof. Liu, UC Berkeley Pole Identification Example 1 w p1 RS Cin EE105 Fall 2007 w p2 Lecture 13, Slide 11 1 RC C L Prof. Liu, UC Berkeley High-Frequency BJT Model • The BJT inherently has junction capacitances which affect its performance at high frequencies. Collector junction: depletion capacitance, Cm Emitter junction: depletion capacitance, Cje, and also diffusion capacitance, Cb. C Cb C je EE105 Fall 2007 Lecture 13, Slide 12 Prof. Liu, UC Berkeley BJT High-Frequency Model (cont’d) • In an integrated circuit, the BJTs are fabricated in the surface region of a Si wafer substrate; another junction exists between the collector and substrate, resulting in substrate junction capacitance, CCS. BJT cross-section EE105 Fall 2007 BJT small-signal model Lecture 13, Slide 13 Prof. Liu, UC Berkeley Example: BJT Capacitances • The various junction capacitances within each BJT are explicitly shown in the circuit diagram on the right. EE105 Fall 2007 Lecture 13, Slide 14 Prof. Liu, UC Berkeley Transit Frequency, fT • The “transit” or “cut-off” frequency, fT, is a measure of the intrinsic speed of a transistor, and is defined as the frequency where the current gain falls to 1. Conceptual set-up to measure fT I out g mVin I in Vin Z in 1 I out 1 g m Z in g m I in jwT Cin g wT m Cin gm 2f T C EE105 Fall 2007 Lecture 13, Slide 15 Prof. Liu, UC Berkeley Dealing with a Floating Capacitance • Recall that a pole is computed by finding the resistance and capacitance between a node and GROUND. • It is not straightforward to compute the pole due to Cm1 in the circuit below, because neither of its terminals is grounded. EE105 Fall 2007 Lecture 13, Slide 16 Prof. Liu, UC Berkeley Miller’s Theorem • If Av is the voltage gain from node 1 to 2, then a floating impedance ZF can be converted to two grounded impedances Z1 and Z2: V1 V2 V1 V1 1 Z1 Z F ZF ZF Z1 V1 V2 1 Av V1 V2 V2 V2 1 Z 2 Z F ZF ZF Z2 V1 V2 1 1 EE105 Fall 2007 Lecture 13, Slide 17 Av Prof. Liu, UC Berkeley Miller Multiplication • Applying Miller’s theorem, we can convert a floating capacitance between the input and output nodes of an amplifier into two grounded capacitances. • The capacitance at the input node is larger than the original floating capacitance. A0 Av Z2 ZF 1 1 1 Av 1 jwCF 1 1 jw 1 1 CF A0 A0 1 ZF 1 jw C F Z1 1 Av 1 A0 jw 1 A0 C F EE105 Fall 2007 Lecture 13, Slide 18 Prof. Liu, UC Berkeley Application of Miller’s Theorem w p ,in 1 RS 1 g m RC C F w p ,out EE105 Fall 2007 1 1 RC 1 g m RC CF Lecture 13, Slide 19 Prof. Liu, UC Berkeley Small-Signal Model for CE Stage EE105 Fall 2007 Lecture 13, Slide 20 Prof. Liu, UC Berkeley … Applying Miller’s Theorem w p ,in 1 RThev Cin 1 g m RC Cm w p ,out 1 1 RC Cout 1 g m RC Cm Note that wp,out > wp,in EE105 Fall 2007 Lecture 13, Slide 21 Prof. Liu, UC Berkeley Direct Analysis of CE Stage • Direct analysis yields slightly different pole locations and an extra zero: gm wz C XY 1 w p1 1 g mRC C XY RThev RThevCin RC C XY Cout 1 g m RC C XY RThev RThev Cin RC C XY Cout w p2 RThev RC CinC XY CoutC XY CinCout EE105 Fall 2007 Lecture 13, Slide 22 Prof. Liu, UC Berkeley Input Impedance of CE Stage 1 Z in || r jwC 1 g m RC Cm EE105 Fall 2007 Lecture 13, Slide 23 Prof. Liu, UC Berkeley