Document 13436429

advertisement

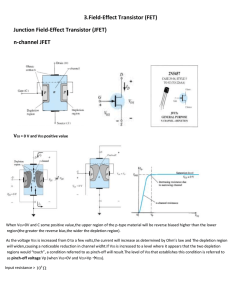

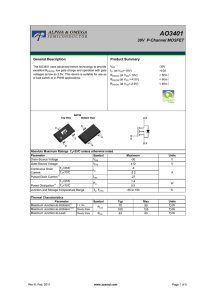

Lecture 10 MOSFET (III) MOSFET Equivalent Circuit Models Outline • Low-frequency small-signal equivalent circuit model • High-frequency small-signal equivalent circuit model Reading Assignment: Howe and Sodini; Chapter 4, Sections 4.5-4.6 6.012 Spring 2009 Lecture 10 1 Large Signal Model for NMOS Transistor Regimes of operation: VDSsat=VGS-VT ID linear saturation I�D VDS VGS VGS VBS VGS=VT 0 0 • Cut-off cutoff VDS ID = 0 • Linear / Triode: ID = • W V μn Cox VGS DS VT • VDS 2 L Saturation W 2 I D = I Dsat = μn Cox [VGS VT ] • [1 + VDS ] 2L Effect of back bias VT (VBS ) = VTo + 6.012 Spring 2009 [ 2p VBS 2p Lecture 10 ] 2 Small-signal device modeling In many applications, we are only interested in the response of the device to a small-signal applied on top of a bias. I�D+id vgs + - VGS + vds + v - bs VBS VDS Key Points: • Small-signal is small – response of non-linear components becomes linear • • Since response is linear, lots of linear circuit techniques such as superposition can be used to determine the circuit response. Notation: iD = ID + id ---Total = DC + Small Signal 6.012 Spring 2009 Lecture 10 3 Mathematically: i D (VGS, VDS , VBS ; v gs , vds , vbs ) I D (VGS , VDS , VBS ) + id (v gs , v ds , vbs ) With id linear on small-signal drives: id = gm vgs + go vds + gmb vbs Define: gm transconductance [S] go output or drain conductance [S] gmb backgate transconductance [S] Approach to computing gm, go, and gmb. gm i D vGS Q go i D vDS g mb Q i D vBS Q Q [vGS = VGS, vDS = VDS, vBS = VBS] 6.012 Spring 2009 Lecture 10 4 Transconductance In saturation regime: W 2 iD = μn Cox [vGS VT ] • [1 + VDS ] 2L Then (neglecting channel length modulation) the transconductance is: gm = i D vGS Q W μn Cox (VGS VT ) L Rewrite in terms of ID: gm = 2 gm 0 6.012 Spring 2009 W μ nCox ID L saturation 0 ID Lecture 10 5 Transconductance (contd.) Equivalent circuit model representation of gm: id G D + vgs S gmvgs - B iD� (μA) 400 ID + id ID 300 id = gmvgs Q 200 100 VGS VDS 1 6.012 Spring 2009 VGS + vgs id 2 3 4 Lecture 10 5 vDS (V) 6 Output conductance In saturation regime: W 2 iD = μnCox [ vGS VT ] • [1 + vDS ] 2L Then: go = iD v DS = Q W 2 μnCox ( VGS VT ) • ID 2L Output resistance is the inverse of output conductance: ro = 1 1 = g o ID Remember also: 1 L Hence: ro L 6.012 Spring 2009 Lecture 10 7 Output conductance (contd.) Equivalent circuit model representation of go: id G D + vgs S iD� (μA) ro - B 400 ID + id ID 300 id = govds id Q 200 vds 100 VDS VDS + vds 1 6.012 Spring 2009 VGS , VBS 2 3 4 Lecture 10 5 VDS (V) 8 Backgate transconductance In saturation regime (neglect channel length modulation): iD W 2 μn Cox [vGS VT ] 2L Then: g mb V W i D = = μn Cox (VGS VT ) • T L v BS Q v BS Q Since: VT (vBS ) = VTo + [ 2p v BS 2p ] Then : VT vBS = Q 2 2p VBS Hence: g mb = 6.012 Spring 2009 gm 2 2 p VBS Lecture 10 9 Backgate transconductance (contd.) Equivalent circuit representation of gmb: id G D + vgs S gmbvbs - vbs B + iD� (μA) 400 ID + id ID 300 Q 200 100 VGS , VBS VDS 1 6.012 Spring 2009 VGS , VBS + vbs id = gmbvbs id 2 3 4 Lecture 10 5 VDS (V) 10 VDS + - VGS Metal interconnect to gate + - n+ polysilicon gate n+ source VBS = 0 0 x y n+ drain QN (y) Xd (y) p-type Metal interconnect to bulk Figure by MIT OpenCourseWare. 6.012 Spring 2009 Lecture 10 6equivalent High-frequency small-signal circuit model Need to add capacitances. In saturation: fringe electric field lines \ source , = b ,' gate ...................................................... ...................................................... ...................................................... ...................................................... ...................................................... ...................................................... ...................................................... ........................... n+ 4k overlap - L ~N(%s) 4k 1% overlap LD depletion] region I Cgs = channel charge + overlap capacitance, C,, Cg, = overlap capacitance, C,, CSb= sourcejunction depletion capacitance (+sidewall) C, = drain junction depletion capacitance (+sidewall) ONLY Channel Charge Capacitance is intrinsic to device operation. All others are parasitic. 6.012 Spring 2009 Lecture 10 Inversion layer charge in saturation L vGS VT 0 0 qN (vGS ) = W QN (y)dy = W dy QN (vC )• • dvC dvC Note that qN is total inversion charge in the channel & vC(y) is the channel voltage. But: iD dvC = dy W μnQN (vC ) Then: W 2 μn qN (vGS ) = • iD VGS VT [QN (vC ) ] • dvC 2 0 Remember: QN (vC ) = Cox [ vGS vC (y) VT ] Then: W μnC qN (vGS ) = iD 2 6.012 Spring 2009 vGS VT 2 ox • [v GS vC (y) VT ] 2 • dvC 0 Lecture 10 13 Inversion layer charge in saturation (contd.) Do integral, substitute iD in saturation and get: 2 qN (vGS ) = WLCox (v GS VT ) 3 Gate charge: qG (vGS ) = q N (v GS ) Q B,max Intrinsic gate-to-source capacitance: Cgs, i = dq G 2 = WLCox dv GS 3 Must add overlap capacitance: 2 C gs = WLC ox + WCov 3 Gate-to-drain capacitance — only overlap capacitance: Cgd = WCov 6.012 Spring 2009 Lecture 10 14 ther capacitances ............... ............... ............... Source-to-Bulk capacitance: c s b = WLdvf cj + (2~di&f + w)cjsw where C : Bottom Wall at Vm (F 1em2 ) Cjsw Side Wall at VSB(F 1 cm) Drain-to-Bulk capacitance: Cdb = WLdiff j + (2~dij-f+ w)cjsw where C j :Bottom Wall at VDB( F I cm2 ) Cjsw Side Wall at VDB(F1cm) Gate-to-Bulk capacitance: 6.012 Spring 2009 Lecture 10 .W What did we learn today? Summary of Key Concepts High-frequency small-signal equivalent circuit model of MOSFET id Cgd G vgs S D + Cgs gmvgs gmbvbs ro - vbs B Cgb Csb + Cdb In saturation: W gm ID L L ro ID Cgs WLCox 6.012 Spring 2009 Lecture 10 16 MIT OpenCourseWare http://ocw.mit.edu 6.012 Microelectronic Devices and Circuits Spring 2009 For information about citing these materials or our Terms of Use, visit: http://ocw.mit.edu/terms.