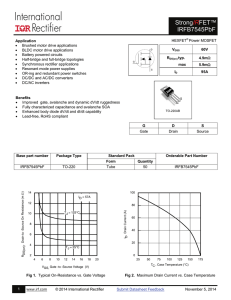

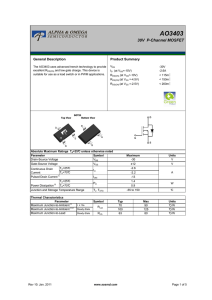

IRFB4615PbF V 150V R

advertisement

PD -96171

IRFB4615PbF

HEXFET® Power MOSFET

Applications

l High Efficiency Synchronous Rectification in SMPS

l Uninterruptible Power Supply

l High Speed Power Switching

l Hard Switched and High Frequency Circuits

D

G

S

VDSS

RDS(on) typ.

max.

ID

150V

32m:

39m:

35A

Benefits

l Improved Gate, Avalanche and Dynamic dV/dt

Ruggedness

l Fully Characterized Capacitance and Avalanche

SOA

l Enhanced body diode dV/dt and dI/dt Capability

l Lead-Free

TO-220AB

IRFB4615PbF

G

D

S

Gate

Drain

Source

Absolute Maximum Ratings

Symbol

ID @ TC = 25°C

ID @ TC = 100°C

IDM

PD @TC = 25°C

VGS

Parameter

Max.

Continuous Drain Current, VGS @ 10V

Continuous Drain Current, VGS @ 10V

35

25

140

144

0.96

± 20

38

-55 to + 175

c

Pulsed Drain Current

Maximum Power Dissipation

Linear Derating Factor

Gate-to-Source Voltage

Peak Diode Recovery

Operating Junction and

Storage Temperature Range

Soldering Temperature, for 10 seconds

(1.6mm from case)

Mounting torque, 6-32 or M3 screw

e

dv/dt

TJ

TSTG

Avalanche Characteristics

EAS (Thermally limited)

IAR

EAR

Single Pulse Avalanche Energy

Avalanche Current

Repetitive Avalanche Energy

c

d

Units

A

W

W/°C

V

V/ns

°C

300

x

x

10lb in (1.1N m)

109

See Fig. 14, 15, 22a, 22b,

f

mJ

A

mJ

Thermal Resistance

Symbol

RθJC

RθCS

RθJA

www.irf.com

Parameter

j

Junction-to-Case

Case-to-Sink, Flat, Greased Surface

Junction-to-Ambient (PCB Mount)

ij

Typ.

Max.

–––

0.50

–––

1.045

Units

°C/W

62

1

09/05/08

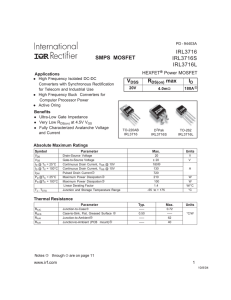

IRFB4615PbF

Static @ TJ = 25°C (unless otherwise specified)

Symbol

Parameter

V(BR)DSS

∆V(BR)DSS/∆TJ

RDS(on)

VGS(th)

IDSS

Drain-to-Source Breakdown Voltage

Breakdown Voltage Temp. Coefficient

Static Drain-to-Source On-Resistance

Gate Threshold Voltage

Drain-to-Source Leakage Current

IGSS

RG(int)

Min. Typ. Max. Units

Conditions

Gate-to-Source Forward Leakage

Gate-to-Source Reverse Leakage

150

–––

–––

3.0

–––

–––

–––

–––

–––

0.19

32

–––

–––

–––

–––

–––

–––

V VGS = 0V, ID = 250µA

––– V/°C Reference to 25°C, ID = 5mA

39

mΩ VGS = 10V, ID = 21A

5.0

V VDS = VGS, ID = 100µA

VDS = 150V, VGS = 0V

20

µA

250

VDS = 150V, VGS = 0V, TJ = 125°C

100

VGS = 20V

nA

VGS = -20V

-100

Internal Gate Resistance

–––

2.7

–––

c

f

Ω

Dynamic @ TJ = 25°C (unless otherwise specified)

Symbol

gfs

Qg

Qgs

Qgd

Qsync

td(on)

tr

td(off)

tf

Ciss

Coss

Crss

Coss eff. (ER)

Coss eff. (TR)

Parameter

Min. Typ. Max. Units

Forward Transconductance

Total Gate Charge

Gate-to-Source Charge

Gate-to-Drain ("Miller") Charge

Total Gate Charge Sync. (Qg - Qgd)

Turn-On Delay Time

Rise Time

Turn-Off Delay Time

Fall Time

Input Capacitance

Output Capacitance

Reverse Transfer Capacitance

h

Effective Output Capacitance (Energy Related)

Effective Output Capacitance (Time Related)

g

35

–––

–––

–––

–––

–––

–––

–––

–––

–––

–––

–––

–––

–––

–––

26

8.6

9.0

17

15

35

25

20

1750

155

40

179

382

–––

–––

–––

–––

–––

–––

–––

–––

–––

–––

–––

–––

–––

Conditions

S

VDS = 50V, ID = 21A

ID = 21A

VDS = 75V

nC

VGS = 10V

ID = 21A, VDS =0V, VGS = 10V

VDD = 98V

ID = 21A

ns

RG = 7.3Ω

VGS = 10V

VGS = 0V

VDS = 50V

(See Fig.5)

pF ƒ = 1.0MHz

VGS = 0V, VDS = 0V to 120V (See Fig.11)

VGS = 0V, VDS = 0V to 120V

f

f

h

g

Diode Characteristics

Symbol

IS

Parameter

Continuous Source Current

VSD

trr

(Body Diode)

Pulsed Source Current

(Body Diode)

Diode Forward Voltage

Reverse Recovery Time

Qrr

Reverse Recovery Charge

IRRM

ton

Reverse Recovery Current

Forward Turn-On Time

ISM

c

Notes:

Repetitive rating; pulse width limited by max. junction

temperature.

Limited by TJmax, starting TJ = 25°C, L = 0.51mH

RG = 25Ω, IAS = 21A, VGS =10V. Part not recommended for use

above this value .

ISD ≤ 21A, di/dt ≤ 549A/µs, VDD ≤ V(BR)DSS, TJ ≤ 175°C.

Pulse width ≤ 400µs; duty cycle ≤ 2%.

2

Min. Typ. Max. Units

–––

–––

35

A

–––

–––

140

Conditions

MOSFET symbol

showing the

integral reverse

D

G

S

p-n junction diode.

––– –––

1.3

V TJ = 25°C, IS = 21A, VGS = 0V

TJ = 25°C

VR = 100V,

–––

70

–––

ns

T

=

125°C

I

–––

83

–––

J

F = 21A

di/dt

= 100A/µs

TJ = 25°C

––– 177 –––

nC

TJ = 125°C

––– 247 –––

–––

4.9

–––

A TJ = 25°C

Intrinsic turn-on time is negligible (turn-on is dominated by LS+LD)

f

f

Coss eff. (TR) is a fixed capacitance that gives the same charging time

as Coss while VDS is rising from 0 to 80% VDSS .

Coss eff. (ER) is a fixed capacitance that gives the same energy as

Coss while VDS is rising from 0 to 80% VDSS.

When mounted on 1" square PCB (FR-4 or G-10 Material). For recom

mended footprint and soldering techniques refer to application

note #AN-994

Rθ is measured at TJ approximately 90°C

www.irf.com

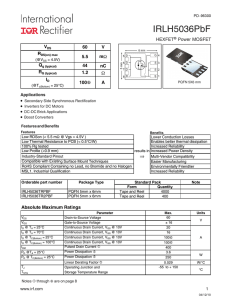

IRFB4615PbF

1000

1000

VGS

15V

12V

10V

8.0V

7.0V

6.0V

5.5V

5.0V

ID, Drain-to-Source Current (A)

100

BOTTOM

10

TOP

ID, Drain-to-Source Current (A)

TOP

1

5.0V

0.1

100

BOTTOM

VGS

15V

12V

10V

8.0V

7.0V

6.0V

5.5V

5.0V

10

5.0V

1

≤60µs PULSE WIDTH

≤60µs PULSE WIDTH

Tj = 25°C

Tj = 175°C

0.1

0.01

0.1

1

10

0.1

100

Fig 1. Typical Output Characteristics

100

3.0

100

RDS(on) , Drain-to-Source On Resistance

(Normalized)

ID, Drain-to-Source Current (A)

10

Fig 2. Typical Output Characteristics

1000

TJ = 175°C

TJ = 25°C

10

1

VDS = 50V

≤60µs PULSE WIDTH

0.1

ID = 21A

VGS = 10V

2.5

2.0

1.5

1.0

0.5

2

4

6

8

10

12

14

16

-60 -40 -20 0 20 40 60 80 100120140160180

T J , Junction Temperature (°C)

VGS, Gate-to-Source Voltage (V)

Fig 4. Normalized On-Resistance vs. Temperature

Fig 3. Typical Transfer Characteristics

100000

14.0

VGS, Gate-to-Source Voltage (V)

VGS = 0V,

f = 1 MHZ

C iss = C gs + C gd, C ds SHORTED

C rss = C gd

C oss = C ds + C gd

10000

C, Capacitance (pF)

1

V DS, Drain-to-Source Voltage (V)

V DS, Drain-to-Source Voltage (V)

Ciss

1000

Coss

Crss

100

10

ID= 21A

12.0

VDS= 120V

VDS= 75V

10.0

VDS= 30V

8.0

6.0

4.0

2.0

0.0

1

10

100

1000

VDS, Drain-to-Source Voltage (V)

Fig 5. Typical Capacitance vs. Drain-to-Source Voltage

www.irf.com

0

5

10

15

20

25

30

35

QG, Total Gate Charge (nC)

Fig 6. Typical Gate Charge vs. Gate-to-Source Voltage

3

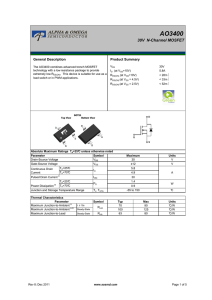

IRFB4615PbF

1000

ID, Drain-to-Source Current (A)

ISD, Reverse Drain Current (A)

1000

100

T J = 175°C

T J = 25°C

10

OPERATION IN THIS AREA

LIMITED BY R DS(on)

100

100µsec

1msec

10

10msec

DC

1

Tc = 25°C

Tj = 175°C

Single Pulse

VGS = 0V

0.1

1.0

0.2

0.4

0.6

0.8

1.0

1.2

1.4

1

1.6

ID, Drain Current (A)

35

30

25

20

15

10

5

0

100

125

150

175

V(BR)DSS , Drain-to-Source Breakdown Voltage (V)

40

75

T C , Case Temperature (°C)

Id = 5mA

185

180

175

170

165

160

155

150

145

140

-60 -40 -20 0 20 40 60 80 100120140160180

Fig 10. Drain-to-Source Breakdown Voltage

3.0

EAS , Single Pulse Avalanche Energy (mJ)

500

2.5

2.0

Energy (µJ)

190

T J , Temperature ( °C )

Fig 9. Maximum Drain Current vs.

Case Temperature

1.5

1.0

0.5

0.0

-20

0

20

40

60

80 100 120 140 160

VDS, Drain-to-Source Voltage (V)

Fig 11. Typical COSS Stored Energy

4

1000

Fig 8. Maximum Safe Operating Area

Fig 7. Typical Source-Drain Diode

Forward Voltage

50

100

VDS, Drain-to-Source Voltage (V)

VSD, Source-to-Drain Voltage (V)

25

10

ID

TOP

2.8A

5.3A

BOTTOM 21A

450

400

350

300

250

200

150

100

50

0

25

50

75

100

125

150

175

Starting T J , Junction Temperature (°C)

Fig 12. Maximum Avalanche Energy vs. DrainCurrent

www.irf.com

IRFB4615PbF

Thermal Response ( Z thJC ) °C/W

10

1

D = 0.50

0.20

0.10

0.05

0.02

0.01

0.1

τJ

R1

R1

τJ

τ1

0.01

R2

R2

R3

R3

τC

τ

τ2

τ1

τ2

τ3

Ci= τi/Ri

Ci i/Ri

1E-005

0.0001

τ4

τ3

τ4

τi (sec)

0.02324

0.000008

0.26212

0.000106

0.50102

0.001115

0.25880

0.005407

Notes:

1. Duty Factor D = t1/t2

2. Peak Tj = P dm x Zthjc + Tc

SINGLE PULSE

( THERMAL RESPONSE )

0.001

1E-006

Ri (°C/W)

R4

R4

0.001

0.01

0.1

t1 , Rectangular Pulse Duration (sec)

Fig 13. Maximum Effective Transient Thermal Impedance, Junction-to-Case

100

Avalanche Current (A)

Duty Cycle = Single Pulse

Allowed avalanche Current vs avalanche

pulsewidth, tav, assuming ∆Tj = 150°C and

Tstart =25°C (Single Pulse)

0.01

10

0.05

0.10

1

Allowed avalanche Current vs avalanche

pulsewidth, tav, assuming ∆Τ j = 25°C and

Tstart = 150°C.

0.1

1.0E-06

1.0E-05

1.0E-04

1.0E-03

1.0E-02

1.0E-01

tav (sec)

Fig 14. Typical Avalanche Current vs.Pulsewidth

EAR , Avalanche Energy (mJ)

120

Notes on Repetitive Avalanche Curves , Figures 14, 15:

(For further info, see AN-1005 at www.irf.com)

1. Avalanche failures assumption:

Purely a thermal phenomenon and failure occurs at a temperature far in

excess of Tjmax. This is validated for every part type.

2. Safe operation in Avalanche is allowed as long asTjmax is not exceeded.

3. Equation below based on circuit and waveforms shown in Figures 16a, 16b.

4. PD (ave) = Average power dissipation per single avalanche pulse.

5. BV = Rated breakdown voltage (1.3 factor accounts for voltage increase

during avalanche).

6. Iav = Allowable avalanche current.

7. ∆T = Allowable rise in junction temperature, not to exceed Tjmax (assumed as

25°C in Figure 14, 15).

tav = Average time in avalanche.

D = Duty cycle in avalanche = tav ·f

ZthJC(D, tav) = Transient thermal resistance, see Figures 13)

TOP

Single Pulse

BOTTOM 1.0% Duty Cycle

ID = 21A

100

80

60

40

20

0

25

50

75

100

125

150

175

Starting T J , Junction Temperature (°C)

PD (ave) = 1/2 ( 1.3·BV·Iav) = DT/ ZthJC

Iav = 2DT/ [1.3·BV·Zth]

EAS (AR) = PD (ave)·tav

Fig 15. Maximum Avalanche Energy vs. Temperature

www.irf.com

5

IRFB4615PbF

30

5.0

4.5

4.0

3.5

ID = 100µA

3.0

ID = 250uA

20

TJ = 25°C

TJ = 125°C

2.0

15

10

ID = 1.0mA

ID = 1.0A

2.5

5

1.5

1.0

0

-75 -50 -25

0

25 50 75 100 125 150 175

0

200

400

600

800

1000

T J , Temperature ( °C )

diF /dt (A/µs)

Fig 16. Threshold Voltage vs. Temperature

Fig. 17 - Typical Recovery Current vs. dif/dt

800

35

30

25

IF = 21A

V R = 100V

700

TJ = 25°C

TJ = 125°C

600

20

QRR (A)

IRR (A)

25

IF = 14A

V R = 100V

5.5

IRR (A)

VGS(th) , Gate threshold Voltage (V)

6.0

15

IF = 14A

V R = 100V

TJ = 25°C

TJ = 125°C

500

400

10

300

5

200

100

0

0

200

400

600

800

0

1000

200

400

600

800

1000

diF /dt (A/µs)

diF /dt (A/µs)

Fig. 19 - Typical Stored Charge vs. dif/dt

Fig. 18 - Typical Recovery Current vs. dif/dt

1000

IF = 21A

V R = 100V

900

800

TJ = 25°C

TJ = 125°C

QRR (A)

700

600

500

400

300

200

100

0

200

400

600

800

1000

diF /dt (A/µs)

6

Fig. 20 - Typical Stored Charge vs. dif/dt

www.irf.com

IRFB4615PbF

Driver Gate Drive

D.U.T

-

-

-

*

D.U.T. ISD Waveform

Reverse

Recovery

Current

+

RG

•

•

•

•

dv/dt controlled by RG

Driver same type as D.U.T.

I SD controlled by Duty Factor "D"

D.U.T. - Device Under Test

VDD

P.W.

Period

VGS=10V

Circuit Layout Considerations

• Low Stray Inductance

• Ground Plane

• Low Leakage Inductance

Current Transformer

+

D=

Period

P.W.

+

+

-

Body Diode Forward

Current

di/dt

D.U.T. VDS Waveform

Diode Recovery

dv/dt

Re-Applied

Voltage

Body Diode

VDD

Forward Drop

Inductor

Current

Inductor Curent

ISD

Ripple ≤ 5%

* VGS = 5V for Logic Level Devices

Fig 21. Peak Diode Recovery dv/dt Test Circuit for N-Channel

HEXFET® Power MOSFETs

V(BR)DSS

15V

DRIVER

L

VDS

tp

D.U.T

RG

VGS

20V

+

V

- DD

IAS

A

0.01Ω

tp

I AS

Fig 22a. Unclamped Inductive Test Circuit

RD

VDS

Fig 22b. Unclamped Inductive Waveforms

VDS

90%

VGS

D.U.T.

RG

+

- VDD

V10V

GS

10%

VGS

Pulse Width ≤ 1 µs

Duty Factor ≤ 0.1 %

td(on)

Fig 23a. Switching Time Test Circuit

tr

t d(off)

Fig 23b. Switching Time Waveforms

Id

Current Regulator

Same Type as D.U.T.

Vds

Vgs

50KΩ

12V

tf

.2µF

.3µF

D.U.T.

+

V

- DS

Vgs(th)

VGS

3mA

IG

ID

Current Sampling Resistors

Fig 24a. Gate Charge Test Circuit

www.irf.com

Qgs1 Qgs2

Qgd

Qgodr

Fig 24b. Gate Charge Waveform

7

IRFB4615PbF

TO-220AB Package Outline

Dimensions are shown in millimeters (inches)

TO-220AB Part Marking Information

(;$03/(

7+,6,6$1,5)

/27&2'(

$66(0%/('21::

,17+($66(0%/</,1(&

,17(51$7,21$/

3$57180%(5

5(&7,),(5

/2*2

'$7(&2'(

1RWH3LQDVVHPEO\OLQHSRVLWLRQ

LQGLFDWHV/HDG)UHH

$66(0%/<

/27&2'(

<($5

:((.

/,1(&

TO-220AB packages are not recommended for Surface Mount Application.

Note: For the most current drawing please refer to IR website at http://www.irf.com/package/

Data and specifications subject to change without notice.

This product has been designed and qualified for the Industrial market.

Qualification Standards can be found on IR’s Web site.

8

IR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245, USA Tel: (310) 252-7105

TAC Fax: (310) 252-7903

Visit us at www.irf.com for sales contact information. 09/2008

www.irf.com