Grad Student Presentation Topics

advertisement

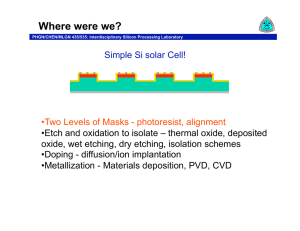

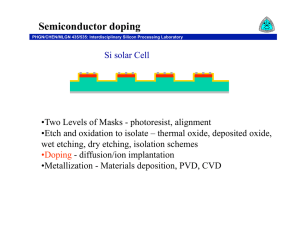

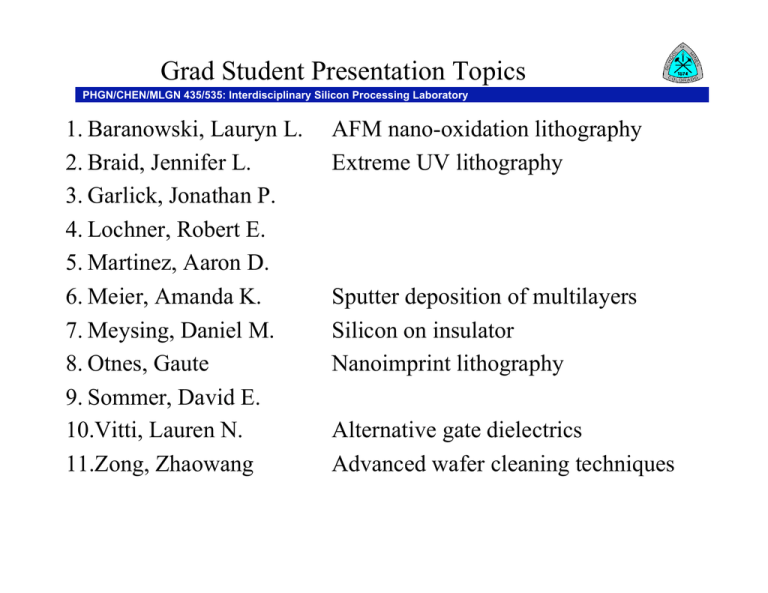

Grad Student Presentation Topics PHGN/CHEN/MLGN 435/535: Interdisciplinary Silicon Processing Laboratory 1.Baranowski, Lauryn L. 2.Braid, Jennifer L. 3.Garlick, Jonathan P. 4.Lochner, Robert E. 5.Martinez, Aaron D. 6.Meier, Amanda K. 7.Meysing, Daniel M. 8.Otnes, Gaute 9.Sommer, David E. 10.Vitti, Lauren N. 11.Zong, Zhaowang AFM nano-oxidation lithography Extreme UV lithography Sputter deposition of multilayers Silicon on insulator Nanoimprint lithography Alternative gate dielectrics Advanced wafer cleaning techniques Logistics PHGN/CHEN/MLGN 435/535: Interdisciplinary Silicon Processing Laboratory • Make up time for faculty absences – Thursday 5? 6? 7? Do one this Thursday? • Presentations Modules 1 and 2 - Tuesday, Feb. 14 in class. Written report due at class time. - Each team will present and provide a written report on the second module they did assembling all results from their section: two presentations on oxidation, two on photoresist. - Presentations will be 10 minutes long (timed and enforced). - Can decide how you want to present, but everyone must speak during the term. There are 3 oral presentations total. Put the name of everyone in your team and the team name on report and presentation. - Reports can be at most 7 pages with 12 pt type and should provide a succinct summary of results, observations, conclusions, recommendations, and any oddities in the process. We want to collect all results as process information for later in the class. - Scoring rubric for talks is on the website as well as example presentations. - Send me talks by 5:00pm Monday Feb. 13 and I will load them up to save transition time. Should be mac/windows neutral. Where were we? PHGN/CHEN/MLGN 435/535: Interdisciplinary Silicon Processing Laboratory Simple Si solar Cell! •Two Levels of Masks - photoresist, alignment •Etch and oxidation to isolate – thermal oxide, deposited oxide, wet etching, dry etching, isolation schemes •Doping - diffusion/ion implantation •Metallization - Materials deposition, PVD, CVD What kind of Mask might we use? PHGN/CHEN/MLGN 435/535: Interdisciplinary Silicon Processing Laboratory Solar Cell Level 1 Level 2 But what if you wanted to make...? Xbox 360 Xenon processor Intel Pentium 4 processor Intel 4004 processor PHGN/CHEN/MLGN 435/535: Interdisciplinary Silicon Processing Laboratory About how many masks are used in a modern integrated circuit process? 1) 2 2) 10 3) 35 4) 100 What is the cost of a single mask set for a modern processor? 1) $1K 2) $10K 3) $100K 4) $millions Number of Mask Levels has also grown Exponentially PHGN/CHEN/MLGN 435/535: Interdisciplinary Silicon Processing Laboratory Lithographic Masks PHGN/CHEN/MLGN 435/535: Interdisciplinary Silicon Processing Laboratory •Lithography accounts for about 1/3 of total IC fabrication cost •Technology performance is often set by lithographic control •From 15-20 different masks in a typical process (up to 36)! •Mask making has become a costly, materials intensive, time consuming process (Cost of a mask set for 45nm node is $2-3M) Masks •Typically made of fused silica •Patterned opaque layer of metal such as Cr •Pattern reduced on wafer during step and repeat process Issues: •Any defect in the mask propagates through all wafers - Cleaning, pellicles, FIB, and laser mask repair •Fused silica loses transparency in deep/deep UV •As features get smaller, thermal control gets more important •Since the mask is the master, how do we pattern the mask? •Direct write processes are slow and get slower! Lithographic Masks cont’d PHGN/CHEN/MLGN 435/535: Interdisciplinary Silicon Processing Laboratory Can we keep using optical masks as long as possible? •Optical proximity correction •Phase shift mask Where were we? PHGN/CHEN/MLGN 435/535: Interdisciplinary Silicon Processing Laboratory Si solar Cell •Two Levels of Masks - photoresist, alignment •Etch and oxidation to isolate – thermal oxide, deposited oxide, wet etching, dry etching, isolation schemes •Doping - diffusion/ion implantation •Metallization - Materials deposition, PVD, CVD Wet etching vs Dry etching PHGN/CHEN/MLGN 435/535: Interdisciplinary Silicon Processing Laboratory Dry etching refers to: 1 Chemical Mechanical Polishing (CMP) 2 Etching in a Gas Plasma 3 Etches that use Dry Ice More likely to be anisotropic 1) wet 2) dry More selective 1) wet 2) dry More likely to create damage 1) wet 2) dry More likely to create contamination 1) wet 2) dry Creates more/dangerous waste 1) wet 2) dry What about etching? PHGN/CHEN/MLGN 435/535: Interdisciplinary Silicon Processing Laboratory Selective Removal of a Material - Goal, exactly transfer the image of a mask layer into the substrate 5 Figures of Merit which Characterize any Etch Process 1. Rate: Faster is generally better but can affect Control 2. Uniformity: Across a wafer and wafer to wafer 3. Isotropy: Usually prefer anisotropic 4. Selectivity: desired rate/rate for other materials 5. Damage: Physical and Chemical Anisotropy PHGN/CHEN/MLGN 435/535: Interdisciplinary Silicon Processing Laboratory Anisotropy: • • A = 0: Perfectly Isotropic A = 1: Perfectly Anisotropic Wet Etching typically more Isotropic Dry Etching typically has anisotropy Over etching Selectivity PHGN/CHEN/MLGN 435/535: Interdisciplinary Silicon Processing Laboratory Sfm: Film to Mask Selectivity Sfs: Film to Substrate Selectivity Sfm Mask Etching Influences Bias Sfs Wet Etching PHGN/CHEN/MLGN 435/535: Interdisciplinary Silicon Processing Laboratory Disadvantages (–) • • • • Generally Isotropic Poor Process Control Contamination Waste Generation Advantages (+) • • • • Highly Selective - example? Little or No Damage Isotropic and anisotropic: MEMS Making a Comeback Can be used in “non-critical” tasks but not practical for features less than 2 microns (we use it a lot). MEMS accelerometer for automobile airbags