EPC2001C – Enhancement Mode Power Transistor V , 100 V R

advertisement

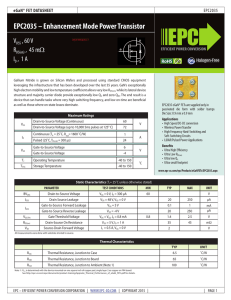

eGaN® FET DATASHEET EPC2001C EPC2001C – Enhancement Mode Power Transistor VDSS , 100 V RDS(on) , 7 mW ID , 36 A NEW PRODUCT EFFICIENT POWER CONVERSION HAL Gallium nitride is grown on silicon wafers and processed using standard CMOS equipment leveraging the infrastructure that has been developed over the last 55 years. GaN’s exceptionally high electron mobility and low temperature coefficient allows very low RDS(on), while its lateral device structure and majority carrier diode provide exceptionally low QG and zero QRR. The end result is a device that can handle tasks where very high switching frequency, and low on-time are beneficial as well as those where on-state losses dominate. Maximum Ratings VDS ID VGS TJ TSTG Drain-to-Source Voltage (Continuous) 100 V Drain-to-Source Voltage (up to 10,000 5ms pulses at 150°C) 120 V Continuous (TA = 25˚C, RθJA = 7.3) 36 Pulsed (25˚C, Tpulse = 300 µs) 150 Gate-to-Source Voltage 6 Gate-to-Source Voltage -4 Operating Temperature -40 to 150 Storage Temperature -40 to 150 EPC2001C eGaN® FETs are supplied only in passivated die form with solder bars Applications • High Speed DC-DC conversion • Class-D Audio • High Frequency Hard-Switching and Soft-Switching Circuits A Benefits • Ultra High Efficiency • Ultra Low RDS(on) • Ultra low QG • Ultra small footprint V ˚C Static Characteristics (TJ= 25˚C unless otherwise stated) TEST CONDITIONS MIN BVDSS PARAMETER Drain-to-Source Voltage VGS = 0 V, ID = 300 µA 100 IDSS Drain Source Leakage VGS = 0 V, V DS = 80 V 100 250 Gate-Source Forward Leakage VGS = 5 V 1 5 Gate-Source Reverse Leakage VGS = -4 V 0.1 0.25 VGS(th) Gate Threshold Voltage VDS = VGS, ID = 5 mA 1.4 2.5 V RDS(on) Drain-Source On Resistance VGS = 5 V, ID = 25 A 5.6 7 mΩ VSD Source-Drain Forward Voltage IS = 0.5 A, VGS = 0 V 1.7 IGSS 0.8 TYP MAX UNIT V µA mA V All measurements were done with substrate shorted to source. Thermal Characteristics TYP RθJC Thermal Resistance, Junction to Case 1 ˚C/W RθJB Thermal Resistance, Junction to Board 2 ˚C/W RθJA Thermal Resistance, Junction to Ambient (Note 1) 54 ˚C/W Note 1: RθJA is determined with the device mounted on one square inch of copper pad, single layer 2 oz copper on FR4 board. See http://epc-co.com/epc/documents/product-training/Appnote_Thermal_Performance_of_eGaN_FETs.pdf for details. EPC – EFFICIENT POWER CONVERSION CORPORATION | WWW.EPC-CO.COM | COPYRIGHT 2014 | | PAGE 1 eGaN® FET DATASHEET EPC2001C Dynamic Characteristics (TJ= 25˚C unless otherwise stated) PARAMETER TEST CONDITIONS MIN TYP MAX 770 900 430 650 15 CISS Input Capacitance COSS Output Capacitance CRSS Reverse Transfer Capacitance 10 RG Gate Resistance 0.3 QG Total Gate Charge VGS = 0 V, V DS = 50 V VDS = 50 V, VGS = 5 V, ID = 25 A QGS Gate-to-Source Charge QGD Gate-to-Drain Charge QG(TH) Gate Charge at Threshold QOSS Output Charge QRR Source-Drain Recovery Charge UNIT pF Ω 7.5 9 2.4 VDS = 50 V, ID = 25 A 1.2 2 nC 1.6 VGS = 0 V, V DS = 50 V 31 45 0 All measurements were done with substrate shorted to source. Figure 1: Typical Output Characteristics at 25°C Figure 2: Transfer Characteristics 150 150 90 60 VGS = 5 V VGS = 4 V VGS = 3 V VGS = 2 V 30 0 0 25 RDS(on) – Drain to Source Resistance (mΩ) ID – Drain Current (A) 120 0.5 1 1.5 2 VDS – Drain-to-Source Voltage (V) 2.5 ID = 10 A ID = 20 A ID = 40 A ID = 80 A 10 5 2 2.5 3 3.5 4 VGS – Gate-to-Source Voltage (V) 60 25 15 0 90 0 3 Figure 3: RDS(on) vs. VGS for Various Currents 20 4.5 VDS = 3 V 30 RDS(on) – Drain to Source Resistance (mΩ) ID – Drain Current (A) 120 25˚C 125˚C 5 0.5 1 1.5 2 2.5 3 3.5 VGS – Gate-to-Source Voltage (V) 4 4.5 5 Figure 4: RDS(on) vs. VGS for Various Temperatures 25˚C 125˚C 20 ID = 25 A 15 10 5 0 2 2.5 EPC – EFFICIENT POWER CONVERSION CORPORATION | WWW.EPC-CO.COM | COPYRIGHT 2014 | 3 3.5 4 VGS – Gate-to-Source Voltage (V) 4.5 5 | PAGE 2 eGaN® FET DATASHEET EPC2001C Figure 5a: Capacitance (Linear Scale) 1.2 Figure 5b: Capacitance (Log Scale) 0.8 Capacitance (nF) Capacitance (nF) 1 COSS = CGD + CSD CISS = CGD + CGS CRSS = CGD 1 0.6 0.4 0.1 COSS = CGD + CSD CISS = CGD + CGS CRSS = CGD 0.01 0.2 0 0 20 40 60 80 100 0.001 0 20 40 VDS – Drain-to-Source Voltage (V) Figure 6: Gate Charge 72 5 ID = 25 A VDS = 50 V 4 3.5 3 2.5 2 1.5 1 0.5 0 0 1 2 3 4 5 6 QG – Gate Charge (nC) 7 48 36 24 12 Figure 8: Normalized On Resistance vs. Temperature 1.5 2 2.5 3 3.5 VSD – Source-to-Drain Voltage (V) 4 4.5 5 Figure 9: Normalized Threshold Voltage vs. Temperature I D = 25 A VGS = 5 V 1.3 Normalized Threshold Voltage Normalized On-State Resistance – RDS(on) 1 1.4 1.6 1.4 1.2 1 0.8 0.6 100 25˚C 125˚C 0.5 8 2 1.8 80 Figure 7: Reverse Drain-Source Characteristics 60 ISD – Source to Drain Current (A) VGS – Gate to Source Voltage (V) 4.5 60 VDS – Drain-to-Source Voltage (V) I D = 5 mA 1.2 1.1 1 0.9 0.8 0.7 0 25 50 75 100 125 TJ – Junction Temperature ( ˚C ) 150 0.6 0 25 50 75 100 125 150 TJ – Junction Temperature ( ˚C ) All measurements were done with substrate shortened to source. EPC – EFFICIENT POWER CONVERSION CORPORATION | WWW.EPC-CO.COM | COPYRIGHT 2014 | | PAGE 3 eGaN® FET DATASHEET EPC2001C 25 Figure 10: Gate Current 25˚C 125˚C IG – Gate Current (mA) 20 15 10 5 0 0 1 2 3 4 5 6 VGS – Gate-to-Source Voltage (V) Figure 11: Transient Thermal Response Curves Junction-to-Board ZθJB, Normalized Thermal Impedance 1 0.1 Duty Factors: 0.5 0.1 0.05 T PDM 0.02 0.01 0.01 Single Pulse 0.001 10-5 tp Notes: Duty Factor = tp/T Peak TJ = PDM x ZθJB x RθJB + TB 10-4 10-3 10-2 tp - Rectangular Pulse Duration [s] 10-1 1 10 Junction-to-Case ZθC, Normalized Thermal Impedance 1 Duty Factors: 0.5 0.2 0.1 0.1 0.05 0.02 0.01 0.01 T PDM 0.001 Notes: Duty Factor = tp/T Peak TJ = PDM x ZθJC x RθJC + TC Single Pulse 0.0001 10-5 tp 10-4 10-3 10-2 tp - Rectangular Pulse Duration [s] 10-1 EPC – EFFICIENT POWER CONVERSION CORPORATION | WWW.EPC-CO.COM | COPYRIGHT 2014 | 1 10 | PAGE 4 eGaN® FET DATASHEET EPC2001C Figure 12: Safe Operating Area I D- Drain Current (A) 100 10 limited by RDS(on) Pulse Width 100 ms 10 ms 1 ms 100 us 1 0.1 0.1 1 10 100 VDS - Drain-Source Voltage (V) TJ = Max Rated, TC = +25°C, Single Pulse TAPE AND REEL CONFIGURATION 4mm pitch, 12mm wide tape on 7” reel b e d f g Loaded Tape Feed Direction Die orientation dot 7” reel c a Gate solder bar is under this corner Die is placed into pocket solder bar side down (face side down) EPC2001C (note 1) Dimension (mm) target min max a b c (note 2) d e f (note 2) g 12.0 1.75 5.50 4.00 4.00 2.00 1.5 11.7 1.65 5.45 3.90 3.90 1.95 1.5 12.3 1.85 5.55 4.10 4.10 2.05 1.6 Note 1: Note 2: MSL1 (moisture sensitivity level 1) classified according to IPC/JEDEC industry standard. Pocket position is relative to the sprocket hole measured as true position of the pocket, not the pocket hole. DIE MARKINGS 2001 YYYY Die orientation dot Gate Pad solder bar is under this corner ZZZZ Part Number EPC2001C Laser Markings Part # Marking Line 1 Lot_Date Code Marking line 2 Lot_Date Code Marking Line 3 2001 YYYY ZZZZ EPC – EFFICIENT POWER CONVERSION CORPORATION | WWW.EPC-CO.COM | COPYRIGHT 2014 | | PAGE 5 eGaN® FET DATASHEET EPC2001C A DIE OUTLINE f Solder Bar View f X9 d X2 DIM 3 4 5 6 7 8 9 10 11 A B c d e f g c B 2 1 e g MIN 4075 1602 1379 577 235 195 400 MICROMETERS Nominal 4105 1632 1382 580 250 200 400 MAX 4135 1662 1385 583 265 205 400 g X8 SEATING PLANE RECOMMENDED LAND PATTERN The land pattern is solder mask defined. 815 Max 100 +/- 20 (685) Side View Pad no. 1 is Gate; (units in µm) Pads no. 3, 5, 7, 9, 11 are Drain; Pads no. 4, 6, 8, 10 are Source; 1362 560 X2 Pad no. 2 is Substrate. 180 X9 180 Efficient Power Conversion Corporation (EPC) reserves the right to make changes without further notice to any products herein to improve reliability, function or design. EPC does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights, nor the rights of others. eGaN® is a registered trademark of Efficient Power Conversion Corporation. U.S. Patents 8,350,294; 8,404,508; 8,431,960; 8,436,398 EPC – EFFICIENT POWER CONVERSION CORPORATION | WWW.EPC-CO.COM | COPYRIGHT 2014 | Information subject to change without notice. Revised October 2014 | PAGE 6