From analog to digital circuits

advertisement

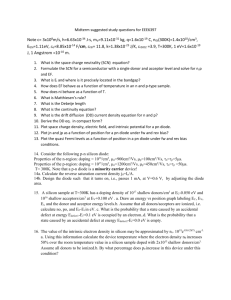

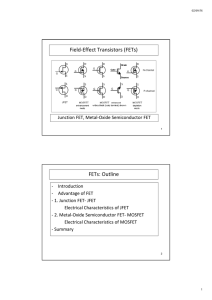

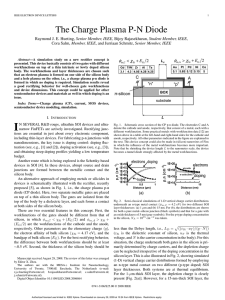

From analog to digital circuits A phenomenological overview Bogdan Roman Outline • • • 2 Insulators, conductors and semiconductors Semiconductor diodes: the p-n junction The Field Effect Transistor (FET): – The Junction FET (JFET) – The Metal Oxide Semiconductor FET (MOSFET) • The MOS Inverter – Resistive and same MOS type – Complementary MOS (CMOS) technology • • • Elementary gates Flip-flops Examples Loosely based on the IA and 3B Engineering dept. courses (Linear Circuits and Devices, Digital Circuits, Information Processing, Integrated Digital Electronics) Insulators and conductors 3 Current I given by: I ne u A V ne A I V L L conductivity ne u E R resistance Mean velocity of electron: u E where = mobility L A Ohm's Law: I V R Semiconductors: Intrinsic silicon At low temperatures, silicon is an insulator since there is not enough thermal energy to break the covalent bonds. At room temperature, the thermal energy kT ~ 1/40 eV is enough to break a few covalent bonds to produce free electrons. This also leaves holes (i.e. positive net charges left by the broken covalent bond). Both electrons and holes contribute to current flow. 4 Semiconductors: Extrinsic silicon electron concentration n electron mobility n hole concentration p hole mobility p n-type conductivity n nen p-type conductivity p pe p when n p then n p 5 The p-n junction: The diode 6 Reverse biased diode: Forward biased diode: The Diode (contd.) Reverse biased diode: 7 Forward biased diode: The Junction Field Effect Transistor (JFET) - Proposed by Shockley in 1951 - First made by Teszner in 1958 in France JFET Interactive (opens browser) 8 Metal Oxide Semiconductor FET (MOSFET) - First made in 1960 at Bell Laboratories in the USA by Atalla and Kahng. - Offers extremely high component density in integrated circuits. - Very high input resistance, low noise, simpler fabrication than bipolar transistors. MOSFET Interactive (opens browser) 9 The NMOS inverter Resistive load: -When input is low (0) then T1 is off, hence output goes high (1) (i.e. VDD) -When VIN = high (1) then T1 conducts (linear region) and brings the output low (0), depending on RL -High RL = low logic zero and low power consumption but large area on silicon and slow switching => compromise 10 NMOS load: - T2 has the gate tied to its drain and is always on (and in saturation). Acts as a pseudo-resistor load. - Similar operation to the resistive load inverter - Smaller area on silicon (so easier to manufacture) and faster switching but has a lower high logic voltage (VDD – VT), and high power consumption when input high. Complementary MOS (CMOS) inverter In CMOS technology, the output is clamped to one of the power rails by a conductive (on) device, while the other device serves as a load of effectively infinite resistance (off). This leads to static properties that approximate those of the ideal inverter. - The PMOS devices is slower (lower mobility of holes) so it has to be larger to compensate. It is also more complex to manufacture. 11 NOR and NAND gates 12 +V +V A B A+B B NOR Gate The 74HC02 IC has four 2-input NOR gates A+B A B A A+B A A B B +V +V A·B NAND Gate A B A·B The 74HC00 IC has four 2-input NAND gates A·B B B A A Flip-flops and clocked flip-flops 13 S = Q S Ck R Master Slave Q Q E R Q Multiplexer A crucial circuit, vital for implementing functions: 14 Binary Counter 15 Current state (ABCD) Next state (ABCD)+ 0000 0001 0001 0010 0010 0011 …. …. 1111 0000 Real stuff 16