Tech3 - Powerpoint Presentation

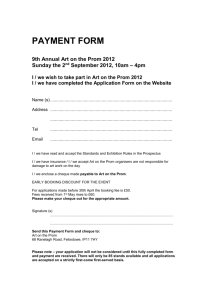

advertisement

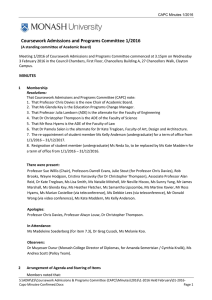

The CAPC Project Tech3 Development April 12, 2002 Introduction What is CAPC? A processor that can perform 15 machine instructions tool – Logic Works Design schedule Development Component integration The Initial Clock “Heart of the system” 8-signal clock Fetch cycle / Execute cycle Registers registers – PC, MAR 16-bit registers – MBR, G, KB, X, Y 4-bit register – IR 12-bit Data Bus & RAM Data transferred along 16-bit data bus Original design – Lab 3 – Write to MBR Second design – Write to RAM Directly Read Only Memory (PROM) Storing program in PROM Updated RAM / PROM hybrid PROM is 1/16k RAM is 4k, but first 1/16k is redundant 000000000000 – 000000111111 PROM >= 000001 000000 RAM Arithmetic Logic Unit 6 operations SEND_NOT, SEND_2X, SEND_ADD, SEND_OR, SEND_XOR, SEND_AND X and Y data input registers; no Z register Keyboard A hexadecimal keyboard that utilizes two registers to send data Integrating Components Machine Instructions – what “And gate” and “OR gate” can do Control Unit Three Is Revolutions lab8’s control unit producing correct signals all the time? Can we restart the clock? How do we prevent the slight chance of faulty signal? CAPC-SP What does SP stand for? Self-Present version of CAPC Introducing the following devices Hex-ASCII translator Machine-Assemble translator Device monitor The first two are simply PROMs and the last one is the combination of PROM and encoder. Conclusion Tech3 develops extreme CAPC Can perform super computations “Einstein” class system Visit the Tech3 site for details http://www.wadanet.com/tech3