MOS Transistors

advertisement

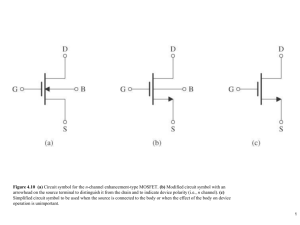

1 Memory SRAM organization • organized as an array of 2M rows ´ 2N columns • Each chip can be organized 1-bit, 4, 8 or 16-bit wide • Eg 64M-bit would be 64M x 1 226 bit address • Storage cells organized as a square array Figure 11.17 A 2M+N-bit memory chip organized as an array of 2M rows ´ 2N columns. 9/15 2 SRAM cell Built with CMOS transistors Used in Cache Sense Amps are used to detect “sense” bit lines that have small signal values Figure 11.23 A differential sense amplifier connected to the bit lines of a particular column. This arrangement can be used directly for SRAMs (which utilize both the B and B lines). DRAMs can be turned into differential circuits by using the “dummy cell” arrangement shown in Fig. 11.25. 9/15 3 NMOS transistor structure Source (S), Drain (D), Gate (G) L channel length, W width of transistor NMOS transistor cross-section Figure 4.1 Physical structure of the enhancement-type NMOS transistor: (a) perspective view; (b) cross-section. Typically L = 0.1 to 3 mm, W = 0.2 to 100 mm, and the thickness of the oxide layer (tox) is in the range of 2 to 50 nm. 9/15 4 NMOS transistor +ve Gate (G) voltage n-channel gate source NMOS Transistor • N-Channel MOSFET • Built on p-type substrate • MOS devices are smaller than BJTs • MOS devices consume less power than BJTs drain Figure 4.2 The enhancement-type NMOS transistor with a positive voltage applied to the gate. An n channel is induced at the top of the substrate beneath the gate. 9/15 5 NMOS transistor iD – VDS +ve VGS > Vt & small VDS ===> resistive device iD VDS Figure 4.4 iD–vDS characteristics of MOSFET in Fig. 4.3 when the voltage applied between drain and source, vDS, is kept small. The device operates as a linear resistor whose value is controlled by v9/15 GS. 6 NMOS transistor +ve VGS > Vt & small VDS ===> acts like resistor Channel induced Figure 4.3 NMOS transistor with vGS > Vt and with a small vDS applied. The device acts as a resistance whose value is determined by vGS. Specifically, the channel conductance is proportional to vGS – Vt’ and thus iD is proportional to (vGS – Vt) vDS. Note that the depletion region is not shown (for simplicity). 9/15 7 NMOS transistor +ve VGS > Vt & increase VDS ===> resistance increases Figure 4.5 Operation enhancement NMOS transistor as vDS is increased. The induced channel acquires tapered shape, its resistance increases as vDS increased. Here vGS is kept constant at a value > Vt. 9/15 8 NMOS transistor id – VDS characteristic +ve VGS …. increase VDS Figure 4.6 The drain current iD versus the drain-to-source voltage vDS for an enhancement-type NMOS transistor operated with vGS > Vt. 9/15 9 Threshold Voltage Vt Value of VG for which channel is “inverted threshold voltage VT (or Vt ) Characteristics of VT • Inverting substrate from p-type to n-type inversion layer in channel • Controlled by inversion in channel • Adjusted by implantation of dopants into the channel • Can be positive or negative • Influenced by the body effect 9/15 10 NMOS circuit symbols (c) Is most common Figure 4.10 (a) Circuit symbol for the n-channel enhancement-type MOSFET. (b) Modified circuit symbol with an arrowhead on the source terminal to distinguish it from the drain and to indicate device polarity (i.e., n channel). (c) Simplified circuit symbol to be used when the source is connected to the body or when the effect of the body on device operation is unimportant. 9/15 11 NMOS transistor, 3 regions Circuit & ID – VDS characteristic For Different VGS Cutoff VGS < Vt Triode VGS > Vt, small VDS Saturation; large VDS, flat ID Figure 4.11 (a) n-channel enhancement-type MOSFET with vGS and vDS applied and with the normal directions of current flow indicated. (b) iD–vDS characteristics for a device with k’n (W/L) = 1.0 9/15 2. mA/V 12 P-channel MOSFET PMOS (c) most common symbol (c) Circuit, with V & I Figure 4.18 (a) Circuit symbol for the p-channel enhancement-type MOSFET. (b) Modified symbol with an arrowhead on the source lead. (c) Simplified circuit symbol for the case where the source is connected to the body. (d) The MOSFET with voltages applied and the directions of current flow indicated. Note that vGS and vDS are negative and iD flows out of the drain terminal. 9/15 13 CMOS structure, today’s ICs both NMOS & PMOS transistors PMOS formed in an n-well Figure 4.9 Cross-section of a CMOS integrated circuit. Note that the PMOS transistor is formed in a separate ntype region, known as an n well. Another arrangement is also possible in which an n-type body is used and the n device is formed in a p well. Not shown are the connections made to the p-type body and to the n well; the latter functions as the body terminal for the p-channel device. 9/15 14 Why CMOS • Advantages • • • • Virtually, no DC power consumed No DC path between power and ground – VDD to load OR load to Gnd Excellent noise margins (VOL=0, VOH=VDD) Inverter has sharp transfer curve • Drawbacks • • • 9/15 Requires more transistors Process is more complicated pMOS size larger to achieve electrical symmetry 15 Digital CMOS Inverter (4.10) Figure 4.53 The CMOS inverter. 9/15 16 Inverter Transfer Characteristic VTC = voltage transfer characteristic Voh Ideal inverter Typical inverter Noise margins NML NMH Vol Vil Vih Voh = output high; Vol = output low; Vil = max input interpreted as “0”; Vih = min input interpreted as “1”; Figure 1.29 The VTC is approximated by three straight line segments. Note the four parameters of the VTC (VOH, VOL, VIL, and VIH) and their use in determining the noise margins (NMH and NML). 9/15 17 CMOS inverter implementation The most common inverter Figure 1.32 A more elaborate implementation of the logic inverter utilizing two complementary switches. This is the basis of the CMOS inverter studied in Section 4.10. 9/15 18 CMOS Inverter – Xfer Curve Figure 4.56 The voltage transfer characteristic of the CMOS inverter. 9/15 19 Other Inverter Implementations All NMOS - Not very popular -- FYI (a) pseudo-NMOS logic inverter. (b) The enhancement-load NMOS inverter. © The depletion-load NMOS inverter. Figure 10.19 (a) The pseudo-NMOS logic inverter. (b) The enhancement-load NMOS inverter. (c) The depletion-load NMOS inverter. 9/15 20