Stick diagrams

advertisement

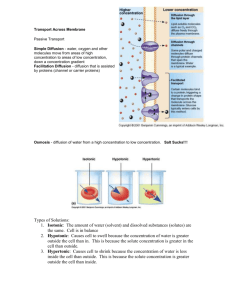

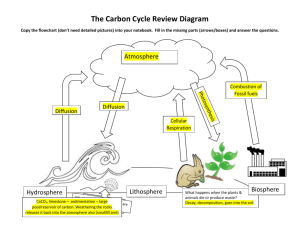

Module-3 (MOS designs,Stick Diagrams,Designrules) Sandeep Radhakrishnan VJEC,Chemperi Before we start…. In this module we are going to study ◦ NMOS and CMOS Design Styles Both combinational and sequential (We had done many examples in our class.So Please go on that.Here I am giving the design of basic gates only) ◦ Stick Diagrams ◦ Layouts ◦ Lamda and micron design rules Transistors as Switches We can view MOS transistors as electrically controlled switches Voltage at gate controls path from g=0 g = 1 source to draind d d nMOS pMOS OFF g ON s s s d d d g OFF ON s s s CMOS Inverter A VDD Y 0 1 A A Y Y GND CMOS Inverter A VDD Y 0 1 OFF 0 A=1 Y=0 ON A Y GND CMOS Inverter A Y 0 1 1 0 VDD ON A=0 Y=1 OFF A Y GND CMOS NAND Gate A B 0 0 0 1 1 0 1 1 Y Y A B CMOS NAND Gate A B Y 0 0 1 0 1 1 0 1 1 ON ON Y=1 A=0 B=0 OFF OFF CMOS NAND Gate A B Y 0 0 1 0 1 1 1 0 1 1 OFF ON Y=1 A=0 B=1 OFF ON CMOS NAND Gate A B Y 0 0 1 0 1 1 1 0 1 1 1 ON A=1 B=0 OFF Y=1 ON OFF CMOS NAND Gate A B Y 0 0 1 0 1 1 1 0 1 1 1 0 OFF A=1 B=1 OFF Y=0 ON ON CMOS NOR Gate A B Y 0 0 1 0 1 0 1 0 0 1 1 0 A B Y VLSI design aims to translate circuit concepts onto silicon. stick diagrams are a means of capturing topography and layer information using simple diagrams. Stick diagrams convey layer information through colour codes (or monochrome encoding). Acts as an interface between symbolic circuit and the actual layout. Stick diagrams A stick diagram is a cartoon of a layout. Does show all components/vias (except possibly tub ties), relative placement. Does not show exact placement, transistor sizes, wire lengths, wire widths, tub boundaries. Stick Diagrams Key idea: "Stick figure cartoon" of a layout Useful for planning layout ◦ ◦ ◦ ◦ relative placement of transistors assignment of signals to layers connections between cells cell hierarchy Stick Diagrams (3/3) Stick Diagrams Stick Diagrams – Notations Metal 1 poly ndiff pdiff Can also draw in shades of gray/line style. Similarly for contacts, via, tub etc.. 17 Stick Diagrams Stick Diagrams – Some rules Rule 1. When two or more ‘sticks’ of the same type cross or touch each other that represents electrical contact. 18 Stick Diagrams Stick Diagrams – Some rules Rule 2. When two or more ‘sticks’ of different type cross or touch each other there is no electrical contact. (If electrical contact is needed we have to show the connection explicitly). 19 Stick Diagrams Stick Diagrams – Some rules Rule 3. When a poly crosses diffusion it represents a transistor. Note: If a contact is shown then it is not a transistor. 20 Stick Diagrams Stick Diagrams – Some rules Rule 4. In CMOS a demarcation line is drawn to avoid touching of p-diff with n-diff. All pMOS must lie on one side of the line and all nMOS will have to be on the other side. 21 Stick diagram -> CMOS transistor circuit Vdd = 5V Vdd = 5V pMOS Vout Vin Vin Vout nMOS In practice, first draw stick diagram for nMOS section and analyse (pMOS is dual of nMOS section) Stick Diagrams Stick Diagrams VDD VDD X x x x X x X X Gnd Gnd 23 Static CMOS NAND gate Static CMOS NOR gate Static CMOS Design Example Layout Draw the stick diagram Identify the Circuit CMOS INVERTER Layout of CMOS NAND Please practice more examples Design Rules Design rules Circuit engineers needs to reduce the size but process engineers needs a controllable and reproducible fabrication So we needs design rules to get more yield. Design rules can never be met exactly at the wafer level because physical nature of semiconductor causes some variations. Parameter limits that cover six standard deviation ensure that 99.7 percentage meets the specification. Design Rules Interface between the circuit designer and process engineer Guidelines for constructing process masks Unit dimension: minimum line width ◦ scalable design rules: lambda parameter ◦ absolute dimensions: micron rules Rules constructed to ensure that design works even when small fab errors (within some tolerance) occur A complete set includes ◦ set of layers ◦ intra-layer: relations between objects in the same layer ◦ inter-layer: relations between objects on different layers Why Have Design Rules? To be able to tolerate some level of fabrication errors such as 1. Mask misalignment 2. Dust 3. Process parameters (e.g., lateral diffusion) 4. Rough surfaces l Based Design Rules Chips are specified with set of masks Minimum dimensions of masks determine transistor size (and hence speed, cost, and power) Feature size f = distance between source and drain ◦ Set by minimum width of polysilicon Feature size improves 30% every 3 years or so Normalize for feature size when describing design rules Express rules in terms of l = f/2 ◦ E.g. l = 0.3 mm in 0.6 mm process 0: Introduction Slid e 37 NMOS Design Rules(l based) Minimum width of PolySi and diffusion line 2l Minimum width of Metal line 3l as metal lines run over a more uneven surface than other conducting layers to ensure their continuity Metal Diffusion 3l 2l 2l Polysilicon Design Rules PolySi – PolySi space 2l Metal - Metal space 2l Diffusion – Diffusion 3l To avoid the possibility of their associated regions overlapping and conducting current Metal 2l Diffusion 2l 3l Polysilicon Design Rules Diffusion – PolySi l Metal lines can pass over both diffusion and polySi without electrical effect. Where no separation is specified, metal lines can overlap or cross Metal Diffusion l Polysilicon Metal Vs PolySi/Diffusion Metal lines can pass over both diffusion and polySi without electrical effect It is recommended practice to leave l between a metal edge and a polySi or diffusion line to which it is not electrically connected Metal l Polysilicon Depletion Transistor We need depletion implant An implant surrounding the Transistor by 2l Ensures that no part of the transistor remains in the enhancement mode A separation of 2l from the gate of an enhancement transistor avoids affecting the device. 2l Depletion Transistor Implants are separated by 2l to prevent them from merging 2l Contact Area must be a min. of 2l*2l to ensure adequate contact area. 2l Contact Area 2l Contact Cut Metal connects to polySi/diffusion by contact cut. Contact area: 2l*2l Metal and polySi or diffusion must overlap this contact area by l so that the two desired conductors encompass the contact area despite any mis-alignment between conducting layers and the contact hole 4l Contact Cut Contact cut – any gate: 2l apart Why? No contact to any part of the gate. 4l 2l Contact Cut Contact cut – contact cut: 2l apart Why? To prevent holes from merging. 2l Nmos Design rules N+Diffusion Mask Diffusion width 2λ Diffusion spacing 3λ Implant Mask Implant gate overlap 1.5λ Implant to enhancement gate spacing 1.5λ Buried contact mask Buried contact to active device 2λ(to avoid short circuit) Overlap in diffusion direction 2λ Overlap in poly or field direction 1λ Buried contact to unrelated poly or diffusion spacing 2λ Poly Mask Poly width 2λ Poly spacing 2λ Poly diffusion spacing 1λ Poly gate extension beyond diffusion 2 λ Diffuin to poly edge 2 λ Contact Mask Contact size 2 λ x 2 λ Contact diffusion overlap 1 λ Contact poly overlap 1 λ Contact to contact space 2 λ Contact to FET channel 2 λ Contact to metal overlap 1 λ Metal mask Metal width 3 λ Metal spacing 3 λ Rules for CMOS layout To ensure the separation of the PMOS and NMOS devices, n-well supporting PMOS is 6l away from the active area of NMOS transistor. Why? Avoids overlap of the associated regions n+ 6l n-well Rules for CMOS layout 2l N-well must completely surround the PMOS device’s active area by 2l 2l Rules for CMOS layout 2l The threshold implant mask covers all n-well and surrounds the n-well by l 2l Rules for CMOS layout The p+ diffusion mask defines the areas to receive a p+ diffusion. It is coincident with the threshold mask surrounding the PMOS transistor but excludes the n-well region to be connected to the supply. 2l 2l Rules for CMOS layout A p+ diffusion is required to effect the ground connection to the substrate. Thus mask also defines this substrate region. It surrounds the conducting material of this contact by l. 4l Simplified Design Rules Conservative rules to get you started 0: Introduction Slid e 55 Micron rules Intra-Layer Design Rule Origins Minimum dimensions (e.g., widths) of objects on each layer to maintain that object after fab ◦ minimum line width is set by the resolution of the patterning process (photolithography) Minimum spaces between objects (that are not related) on the same layer to ensure they will not short after fab 0.3 micron 0.15 0.15 0.3 micron Intra-Layer Design Rules Same Potential 0 or 6 Well Different Potential 2 9 Polysilicon 2 10 3 Active Contact or Via Hole 3 2 Select 3 Metal1 2 2 3 4 Metal2 3 Transistor Transistor Layout 1 3 2 5 Select Layer 2 3 Select 2 1 3 3 2 Substrate 5 Well Please refer the text for more details about the design rules…. Text:VLSI Technology Author:Sujatha Pandey and Manoj Pandey Page No.:5.36 to 5.44