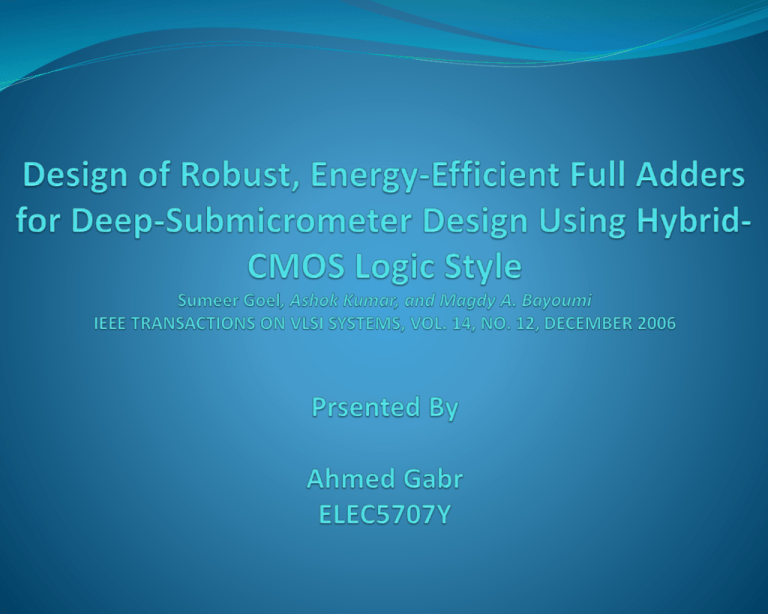

The Software Defined radio: Fact and Fiction

advertisement

Introduction Why Full adders are important? Modern portable electronics require: Smaller silicon area, Higher speeds, Longer battery life, and More reliability Adders are an extensively used component in datapaths. Different Logic Styles Static CMOS Existence of pMOS which has low mobility compared to nMOS High Input capacitance. Complementary Pass Transistor (CPL) Large power consumption. Layout is not easy due to irregular transistor arrangement. Transmission-function full adder (TFA) Transmission-gate full adder (TGA) Lack driving capability. Dynamic CMOS Higher switching activity and lower noise immunity. Large portion of the power in driving the clock lines More susceptible to leakage Hybrid Logic Styles Use more than one logic style for their implementation. Categorization of Full-Adder The outputs of a 1-b full adder can be generally expressed as The three broad categories are as follows A. B. C. XOR–XOR-Based Full Adder XNOR–XNOR-Based Full Adder Centralized Full Adder XOR–XOR-Based Full Adder The general form of this category is expressed as follows, Where H is and is the complement of H. XONR–XONR-Based Full Adder The general form of this category is expressed as follows, Centralized Full Adder The general form of this category is expressed as follows, Module I Proposed XOR-XNOR circuit Based on CPL logic using only one inverter. Cross-coupled pMOS transistors guarantees Full swing operation and reduce short circuit current Module I Comparison Module II Different circuits are compared The circuit shown in figure is one of the best performance and has Good driving capabilities No Short Circuit currents Module III The output can be expressed as TG logic style is used as they consume very low power. Static-CMOS logic style also used because of its robustness and good noise margins The carry is evaluated using the following logic expression Module III Comparison Full Adder Module II Module I Module III Simulation Setup Circuit layout is extracted using TSMC 0.18µm technology. All the possible input combinations are considered for all the test circuits All the simulated circuits are prototyped at optimum transistor sizing The circuits are tested for a range of supply voltages (0.8–1.8 V) at 50-MHz frequency Different loading conditions to evaluate the performance of the test circuits (5.6–200 fF) Each adder is embedded in a 4- and 8-b 4-operand carry–save array adder (CSA) with final carry–propagate adder (CPA). Simulation Results: Delay TFA and TGA have the smallest delays CMOS is ahead of the CPL adder . HPSC and NEW14T adders perform poorly at low voltages Speed degrades significantly at higher loads for TGA and TFA. CMOS shows the least speed degradation. Simulation Results: Power The CPL adder dissipates the most power TGA and TFA dissipate least power. The proposed full adder and NEW-HPSC adder have the least power dissipation. TFA and TGA show degradation than others. more Simulation Results: Summary Simulation results for the proposed full adder in 0.18µm technology at 50-MHz frequency and 1.8V VDD 4-operand CSA with final CPA. Simulation Results for Four-Operand CSA As the number of bits of the operands increase, the power dissipated in the CSA increases proportionally. The adders without driving capability (TGA and TFA) show the poorest performance Conclusion Hybrid-CMOS design style gives flexibility for the designer. The proposed hybrid-CMOS full adder performs well with supply voltage scaling and under different load conditions Hybrid-CMOS design style is recommended for the design of high-performance circuits.