ex1c digital circuits and systems

advertisement

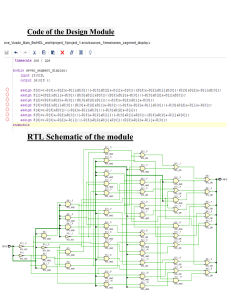

EX1C DIGITAL CIRCUITS AND SYSTEMS 6-bit adder substractor TEAM NUMBER: ___________ Due date:________ Active members Roles: (reporter, simulator, etc.) (1) ________________________________________ (2) _________________________________________ (3) _________________________________________ _______________ _______________ _______________ You have to use this template in order to solve the EX1C, that appears in the site digsys.upc.es. Read the EX1C.docx and follow the instructions of your instructor in order to present the results. 1- Abstract (outline in English the most relevant results and the tools you have used to solve the exercise, 10 lines minimum) 2- Objectives (indicate 5 objectives minimum, in English) 3- Solution to the questions, analysis, designs, projects (Include a brief description of each question) A- Do a gate level simulation of one_bit_adder.vhd (Unit 1.7). Device: Spartan-3E XC3S500E-FG320 (FPGA chip included in Nexys2 board) Your text here ……… B- Do a gate level simulation of four_bit_adder.vhd (Unit 1.7). Your text here ……… C- Do a gate level simulation of design 2 (minilog.exe) and design 5 (Hierarchical design) of EX1B, corresponding to the output M. Compare the delays and indicate the maximum delay between the inputs and the outputs and the maximum frequency of operation of each circuit. Implement the stimulus (test bench file) of this truth table with ISIM: S1 S0 B A Time(s) 0 0 0 0 10 0 0 1 0 20 0 1 0 1 10 1 1 0 0 20 1 1 1 1 40 Your text here ……… D- Read the notes.pdf of 1-Digit BCD Adder Substractor (12-13Q2). Implement in ISE-WEBPACK the structure of 1-Digit BCD Adder Substractor, without programming the architecture of each module. Obtain the RTL viewer. Explain briefly the function of each module. Your text here ……… E- Implement a 6-bit adder substractor. - Draw the entity of the circuit - VHDL code - RTL scheme - Indicate the stimulus of the test bench file (.vht) Implement the stimulus of this truth table with Active HDL: B A OP Time(s) 00000 00000 0 20 10101 00000 0 10 0x0B 0x01 1 20 11111 00010 0 10 0x05 0x0F 1 20 0x08 0x02 0 40 - Functional simulation with ISIM (Timing diagram) - Gate level simulation with ISIM (Timing diagram). Indicate the maximum delay between the inputs and the outputs and the maximum frequency of operation of the circuit. - Justify the results F- Change to the device XC2C256-TQ144, which is included in the CoolRuner CPLD starter board. Compare the delays with those obtained in section E. Use the same test bench file. Your text here ……… 4- Dedication time to solve the exercise (in hours) Individual In group Member 1 Member 2 Member 3 5- Selfassessment Member 1 Member 2 Member 3 6- Reflection about the development of the exercise(Describe the meetings outside the class, difficulties in solving the exercise, etc) Your text here ……… 7- References(indicate the references