Digital Integrated Circuits A Design Perspective

advertisement

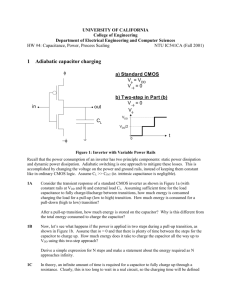

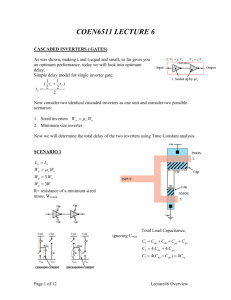

Digital Integrated Circuits A Design Perspective Jan M. Rabaey Anantha Chandrakasan Borivoje Nikolic The Inverter Revised from Digital Integrated Circuits, © Jan M. Rabaey el, 2002 © Digital Integrated Circuits2nd Inverter Power Dissipation © Digital Integrated Circuits2nd Inverter Where Does Power Go in CMOS? • Dynamic Power Consumption Charging and Discharging Capacitors • Short Circuit Currents Short Circuit Path between Supply Rails during Switching • Leakage Leaking diodes and transistors © Digital Integrated Circuits2nd Inverter Vdd E0->1 = C LVdd2 A First-Order RC Network isupply PMOS A1 R NETWORK AN NMOS vdd NETWORK T E 01 Vout CL CL Vdd T = P t dt = V i t dt = V dd sup ply dd 0 0 T E vout T = P t dt = V i t dt = ca p cap out ca p 0 0 0 C dV = C V 2 L out L dd Vdd 1 2 -C V C L Vout dVout = -dd 2 L 0 • Only half of the energy supplied by the power source is stored on load. The other half is dissipated by the PMOS transistor. • It is independent of size when load capacitor dominates!!! © Digital Integrated Circuits2nd Inverter Dynamic Power Dissipation Vdd Vin Vout CL Energy/transition = CL * Vdd2 Power = Energy/transition * f = CL * Vdd2 * f Need to reduce CL, Vdd, and f to reduce power. © Digital Integrated Circuits2nd Inverter Modification for Circuits with Reduced Swing Vdd Vdd Vdd -Vt CL E0 1 = CL Vdd Vdd – Vt Can exploit reduced sw ing to low er power (e.g., reduced bit-line swing in memory) © Digital Integrated Circuits2nd Inverter Node Transition Activity and Power Consider switching a CMOS gate for N clock cycles E = C V 2 n N N L dd EN : the energ y consumed for N clock cycles n(N ): the number o f 0->1 transition in N clock cycles EN 2 n N P = lim -------- f = lim ------------ C V f clk a vg N clk dd N N N L 0 1 = P © Digital Integrated Circuits2nd av g n N lim -----------N N Switching factor = C V 2 f 0 1 L dd clk Inverter Transistor Sizing for Minimum Energy (1) In Out Cg1 1 f Cext Cext/Cg1=F Minimizing energy without delay constraints is not meaningful Goal: Minimize Energy of whole circuit with Design parameters: f and VDD tp tpref of circuit with f = 1 and VDD =Vref f F t p t p 0 1 1 , f © Digital Integrated Circuits2nd t p0 VDD VDD VTE Inverter Transistor Sizing for energy (2) Performance Constraint (when =1) tp t pref t p0 t p 0 ref F 2 f f VDD Vref VTE 3 F Vref VDD VTE F 2 f f 1 3 F Energy for single Transition (when =1) 2 E VDD C g1 1 1 f F 2 VDD 2 2 f F E Eref Vref 4 F © Digital Integrated Circuits2nd Gate: Cg1 Intrinsic: γCg1 Gate: f Cg1 Intrinsic: f γ Cg1 Inverter Transistor Sizing for energy (3) E/Eref=f(f), Vref=2.5V, VDD =M(f) VDD =M(f), VTE=0.5V, Vref=2.5V 4 1.5 F=1 3.5 normalized energy F=1 3 2 vdd (V) 2.5 5 2 10 1.5 1 1 0.5 20 0.5 0 1 2 3 4 f 5 6 7 0 1 2 3 4 5 6 7 f This plots what energy ratio This plots what VDD can be is if using VDD derived if delay constraint is met Every point here has the same delay for given F © Digital Integrated Circuits2nd Inverter Transistor Sizing for energy (4) Device sizing together with VDD scaling is very effective to reduce power consumption Over-sizing does not pay back in terms of both delay and power consumption (design for right speed, not maximum) Optimal sizing for energy is smaller than the one for delay © Digital Integrated Circuits2nd Inverter Short Circuit Currents Vd d Vin Vout t sc CL The time duration when both devices on Peak current is directly proportional to sizes !!! 0.15 IVDD (mA) Pdp VDD I peak t sc f 0 1 0.10 0.05 0.0 1.0 © Digital Integrated Circuits2nd 2.0 3.0 Vin (V) 4.0 5.0 Inverter How to keep Short-Circuit Currents Low? Short circuit current goes to zero if tfall >> trise, why? Large load capacitance cause large rise time but can’t do this for cascade logic, since making the output rise/fall too large slows down the later gates and can cause short circuit current for those gates. (global picture is important!!!) © Digital Integrated Circuits2nd Inverter Minimizing Short-Circuit Power 8 7 6 Vdd =3.3 Pnorm 5 4 Vdd =2.5 3 2 1 0 Vdd =1.5 0 1 2 3 4 5 t /t sin sout © Digital Integrated Circuits2nd Inverter Static power consumption: Leakage Pstat I statVDD Vd d Vout N+ Drain Junction Leakage Sub-Threshold Current P-sub Sub-threshold current one of most compelling issues Sub-Threshold in low-energy circuitCurrent design!Dominant Factor © Digital Integrated Circuits2nd Inverter Reverse-Biased Diode Leakage GATE p+ p+ N Vdd Reverse Leakage Current + V - dd IDL = JS A • diode leakage caused by thermally generated carriers! 2 = 1-5pA/ m for a 1.2m CMOS •JJS = 10-100 pA/m2 at 25technology deg C for 0.25m CMOS! S o doubles for every 9 deg C! JJS s double with every 9 C increase in temperature • At 85 degrees, a commonly imposed upper bound for junction temperatures in commercial hardware products, the leakage current increase by a factor of 60 over the 25 deg. © Digital Integrated Circuits2nd Inverter Subthreshold Leakage Component © Digital Integrated Circuits2nd Inverter Principles for Power Reduction Prime choice: Reduce voltage! Recent years have seen an acceleration in supply voltage reduction Design at very low voltages still open question (0.6 … 0.9 V by 201x?) Reduce switching activity (very difficult!) Reduce physical capacitance Device Sizing: for F=20 – fopt(energy)=3.5, fopt(performance)=4 © Digital Integrated Circuits2nd Inverter Performance measure of inverter Total power consumption 2 Ptotal Pdyn Pdp Pstat (C LVDD VDD I peak t s ) f 0 1 VDD I leak Power-delay product PDP gives a measure of energy, as from the units (w*s=Joule). Assuming inverter operating at its maximum switching frequency f max 1 /( 2t p ), 2 2 PDP C LVDD f max t p C LVDD / 2 Eav 2 PDP Energy-delay product (misconception about VDD in PDP) A more relevant metric showing tradeoff between power and parameter performance (delay) C LVDD 2 EDP PDP t p C LVDD t p / 2, tp VDD VT VDSAT / 2 2 3 C L VDD EDP VDD,opt 3(VT VDSAT / 2) / 2 2(VDD VT VDSAT / 2) 2nd © Digital Integrated Circuits Inverter © Digital Integrated Circuits2nd Inverter Impact of Technology Scaling 10μm to 23nm © Digital Integrated Circuits2nd Inverter Goals of Technology Scaling Make things cheaper: Want to sell more functions (transistors) per chip for the same money Build same products cheaper, sell the same part for less money Price of a transistor is reduced ? But also want to be faster, smaller, lower power, lighter Reduce gate delay Increase transistor density Reduce energy per transition © Digital Integrated Circuits2nd Inverter Technology Scaling Die size is used to increase by 14% per generation Technology © Digital Integrated Circuits2nd generation spans 2-3 years Inverter Technology Evolution International Technology Roadmap for Semiconductors Year of Introduction 1999 Technology node [nm] 180 Supply [V] 2000 2001 2004 2008 2011 2014 130 90 60 40 30 0.6-0.9 0.5-0.6 0.3-0.6 8 9 9-10 10 3.5-2 7.1-2.5 11-3 14.9 -3.6 1.5-1.8 1.5-1.8 1.2-1.5 0.9-1.2 Wiring levels 6-7 6-7 7 Max frequency [GHz],Local-Global 1.2 Max P power [W] 90 106 130 160 171 177 186 Bat. power [W] 1.4 1.7 2.0 2.4 2.1 2.3 2.5 1.6-1.4 2.1-1.6 Node years: 2007/65nm, 2010/45nm, 2013/33nm, 2016/13nm © Digital Integrated Circuits2nd Inverter Technology Evolution © Digital Integrated Circuits2nd Inverter Technology Scaling (1) Minimum Feature Size (micron) 10 10 10 10 2 1 0 -1 -2 10 1960 1970 1980 1990 2000 2010 Year Minimum Feature Size © Digital Integrated Circuits2nd Inverter Technology Scaling (2) Number of components per chip © Digital Integrated Circuits2nd Inverter Technology Scaling (3) tp decreases by 13%/year 50% every 5 years! © Digital Integrated Circuits2nd Inverter Technology Scaling (4) / 4 x 3 1 0.1 0.01 80 MPU DSP 85 90 Year (a) Power dissipation vs. year. 95 1000 3 10 ars e y 0.7 100 Power Dissipation (W) 100 rs Power Density (mW/mm2 ) ea x 1.4 / 3 y 10 1 1 Scaling Factor (normalized by 4 m design rule ) (b) Power density vs. scaling factor. From Kuroda © Digital Integrated Circuits2nd Inverter 10 Processor Scaling P.Gelsinger: “Processors for the New Millenium”, ISSCC 2001 © Digital Integrated Circuits2nd Inverter Processor Power P.Gelsinger: Processors for the New Millenium, ISSCC 2001 © Digital Integrated Circuits2nd Inverter Processor Performance P.Gelsinger: Processors for the New Millenium, ISSCC 2001 © Digital Integrated Circuits2nd Inverter Technology Scaling Models • Full Scaling (Constant Electrical Field) ideal model — dimensions and voltage scale together by the same factor S • Fixed Voltage Scaling most common model until recently — only dimensions scale, voltages remain constant • General Scaling most realistic for todays situation — voltages and dimensions scale with different factors © Digital Integrated Circuits2nd Inverter Scaling (long Channel Devices) © Digital Integrated Circuits2nd Inverter Scaling (short-channel devices) © Digital Integrated Circuits2nd Inverter Scaling (short-channel devices) k n' n Cox n ox tox W kn k L 2 V W I sat k n' ((VGS VT )VDSAT DSAT ) L 2 V W k n' VDSAT ((VGS VT ) DSAT ) L 2 VDSAT ' k nW sat ((VGS VT ) ) 2 ' n © Digital Integrated Circuits2nd Inverter 2016 Outlook Performance 2X/16 months 1 TIP (terra instructions/s)? 2GHz VS 30GHz clock (building super-computers with multi-core maybe the promising solution!!!)? Size No of transistors: 10 Billion? Die: 60*60 mm? Power Total <200mW ? Leakage: more than 1/3 of the active Power? © Digital Integrated Circuits2nd P.Gelsinger: Processors for the New Millenium, ISSCC 2001 Inverter Questions What will cause this model to break? Power and power density Leakage Process Variation When will it break? Will the model gradually slow down? Dead of CMOS? New technology? © Digital Integrated Circuits2nd Inverter