MS Word

advertisement

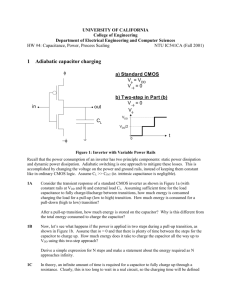

UNIVERSITY OF CALIFORNIA College of Engineering Department of Electrical Engineering and Computer Sciences Last modified on February 9, 2006 by Seng Oon Toh (sengoon@eecs) Borivoje Nikolic Homework #4:, Delay, Power Dissipation and Process Scaling EECS 141 Problem #1: Propagation Delay and Energy a) What is the delay of a minimum sized inverter driving another inverter f times its size? For the minimum sized inverter, assume input capacitance equal to Cunit and equivalent resistance through the NMOS or PMOS equal to Runit. Let’s say the folks in EE 130 did a good job and managed to reduce the intrinsic (self-loading) capacitance on the output to ½ Cunit. Assume that the capacitance and resistance values scale linearly with size. Your answer will be in terms of these parameters (no calculations!). Take the limit as f goes to 0 and call the result inv. b) From part (a), how much energy is consumed by the driving inverter after successive low to high (L→H) and high to low (H→L) transitions, in terms of a supply voltage Vdd? c) In order to drive a large capacitance (CL=70Cunit) from a minimum size gate (with input capacitance Cin= Cunit), you decided to introduce a two-stage buffer as shown in Fig. 1. From (a), the propagation delay of a self-loaded minimum size inverter is inv. Assume that the capacitance and resistance values scale linearly with size. Determine the sizing of the two additional buffer stages that will minimize the propagation delay. What is the corresponding propagation delay? Fig. 1: Buffer Chain d) Given a supply voltage of Vdd, and a probability of input going from zero to one P01=0.5, what is the average energy-delay product of the circuit in part (c)? e) Determine the sizing of the two buffer stages that will minimize the average energy per transition while maintaining the propagation delay within 10% of the minimum value from part (c). For simplicity, assume that sizes are increasing in geometric fashion (1, f, f2). This means that effective fanout of the first two stages (Cin2/Cin and Cin3/Cin2) is f, while the effective fanout of the last stage is equal to CL/Cin3. What is the new average energy-delay product? 1 f) Find the optimum number of inverters and sizing ratio for the output load specified in Part (c). Express the optimum delay in terms of inv. Considering your result for Part (b), do you think this inverter chain will consume more or less energy than a single inverter driving the output load? Problem #2: Equivalent RC models In class we modeled the inverter delay by finding its equivalent resistance and capacitance. You are asked to find the equivalent resistance and input capacitance of a capacitively loaded symmetrically sized inverter. a) Draw a schematic of how you would measure the equivalent resistance and briefly explain how you would do this.. b) Draw a schematic of how you would measure the equivalent input capacitance of this inverter. Explain the measurement procedure. c) Does the input capacitance of this inverter depend on its loading? Explain your answer. d) Does the input capacitance of this inverter depend on the type of input transition (H-L or L-H transition)? If the answer is yes, which one is larger? Explain your answer. 2 Problem #3: Transistor Ratio, Switching Point and SPICE So far we’ve defined the switching point to be 50 % of Vdd. It turns out that modern CMOS standard cell databooks have been using lower switching points. In this problem, we will discover why this is so. a) Based on extracted parameters in Table 3-2 of the textbook, calculate the PMOS/NMOS ratio (β = Wpmos/Wnmos) such that VM = Vdd/2 = 1.25 V. Verify your calculation by simulating the VTC of an inverter sized with this ratio. Use the models referenced in Homework 2 under the TT (normal-normal) process corner. Make your NMOS “minimum sized” (W=0.36u, L=0.24u). b) Simulate a 5 stage ring-oscillator sized according to part (a). Measure tpHL, tpLH, and tosc(oscillation period) across switching points from 40% Vdd to 60% Vdd in 5% steps (i.e. 40% Vdd, 45% Vdd etc.). Which switching point equalizes tpHL and tpLH? Make sure to include area and drain parameters in your SPICE deck. Use W=0.48um and L=0.24 um for the NMOS to simplify area and parameter calculations and since we’re not going to allow dog-bone transistors in our layouts. Hint: 1) Use the .param statement to define variables (beta, width, swpoint, etc.) so that these variables can be swept 2) Construct an inverter using the .subckt statement and reuse the macro to construct the ring-oscillator 3) Use the .measure statement to automatically measure and report the delays 4) Set the initial condition on one of the nodes to Vdd to ‘kick-start’ the oscillator (look at the .ic and uic keywords) 5) Use the sweep feature of the .tran statement to sweep the switching point variable c) Calculate β such that tosc is minimum in a ring oscillator. Make sure to include intrinsic capacitance and loading of the next gate. d) Sweep β to verify the calculation in part (c). Why does a smaller value of β produce minimum tosc? What are the tradeoffs in choosing a smaller β over the ratio calculated in part (a)? e) Using the value of β found in part (d), measure tpHL and tpLH using switching points from 40% to 60%. Which switching point would you use to specify a standard cell library designed with this ratio? Why? 3