L6_Overview

advertisement

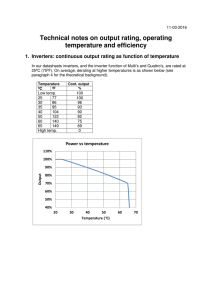

COEN6511 LECTURE 6 CASCADED INVERTERS ( GATES) As was shown, making tr and tf equal and small, so far gives you an optimum performance, today we will look into optimum delay. Simple delay model for single inverter gate: 1 1 ( tr t f ) 2 td 2 2 Now consider two identical cascaded inverters as one unit and consider two possible scenarios: 1. Sized inverters W p r .Wn 2. Minimum size inverter Now we will determine the total delay of the two inverters using Time Constant analysis. SCENARIO 1 L p Ln W p r .Wn W p 3.Wn W p 3W R= resistance of a minimum sized nmos, Wn,min Total Load Capacitance, ignoring Cwire Cl Cdp Cdn C gp C gn Cl 4.C dn 4.C gn Cl 4(Cdp Cgn ) 4Ceq Page 1 of 12 Lecture#6 Overview Let Cdn + Cgn = Ceq, time constant analysis: T Tr T f T R * 4Ceq R * 4Ceq Scenario 1 T 8RC eq SCENARIO 2, MINIMUM SIZE INVERTER Let R be the resistance of minimum size NMOS as before, R p 3 Rn 3R Cdp Cdn C gp C gn C Cdp Cdn C gp C gn C 2.C d 2.C g C 2Ceq Time constant: T Tr T f T 3R 2Ceq R * 2Ceq Scenario 2 T 8RC eq Design Guidelines For cascaded inverters (gates), minimum sized inverters gives the same delay as the r sized inverters Minimum area is obtained for Scenario 2 configuration Watchout, tr and tf are not equal Watchout VTC characteristic is shifted and that affects noise margin distribution Page 2 of 12 Lecture#6 Overview Next Question: What is the optimum Aspect ratio (Wp/Wn) that gives minimum delay when an inverter drives another inverter? OPTIMUM WIDTH RATIO Assume two identical and cascaded CMOS inverters, Then, considering the load we can write approximately the logical efforts required proportional to the switching activity as must turn off load must turn off ZWn1 Wn 2 ZWn 2 Wn 2 nWn1 Z pWn 2 must turn on must turn on Also W ZWn 2 Wn 2 zWn 2 n1 Z pWn1 nWn 2 ↓ indicates delay when the input signal goes low. ↑ indicates delay when the input signal goes high. If we express the delay in the above manner and differentiate with respect to Z, we get the optimum Zopt = delay , Z n r p If we take the wire capacitance, Cw, into account, Zopt = n Cw (1 ) p Cdn1 C g 2 Also, if the second inverter was larger by t, more than the first then Zopt = r 1 2t 2t Design Guidelines: Page 3 of 12 Lecture#6 Overview For optimum delay, size your inverters as W p r and for our process, W p 1.73Wn For short distances, size W p 2Wn so as to get optimum delay. Watchout that this will result in a non-symmetrical VTC and noise margins Watchout the parameters tr and tf are not equal and not fast enough, that is, tr will be twice tf. POWER CONSUMPTION IN CMOS CIRCUITS Two Components contribute to the power dissipation: Static Power Dissipation – Leakage current – Sub-threshold current Dynamic Power Dissipation – Short circuit power dissipation – Charging and discharging power dissipation Static Power Dissipation Leakage Current: Looking into the CMOS inverter below shows that the leakage current is mainly due to P-N junction reverse biased current. Typical value 0.1nA to 0.5nA @room temp. Page 4 of 12 Lecture#6 Overview The leakage current IL for each diode is obtained by: qV kT I L I S (e 1) , I S is obtained from the process manual. It is possible to estimate leakage current for a gate or for the circuit. n Ps leakage current * supply vol tage 1 Sub-threshold Current • Relatively high in low threshold device Sub-threshold current is prominent in short devices. Current starts to flow in small quantities when Vin is approaching Vt. Page 5 of 12 Lecture#6 Overview DYNAMIC POWER DISSIPATION Short circuit current: A. B. C. D. Input VTC Current flow Current flow when load is increased As can be seen during transition due to input signal whenever the pmos and nmos are both are on, then a direct path exists between Vdd and Vss. Page 6 of 12 Lecture#6 Overview For tr=tf = trf VTN=|VTP| The short circuit power dissipation: I (Vdd 2Vt ) 3 ( tr , f ) 12 tp Heavier loads also contribute. The model above indicates the short circuit current without load condition. So it mainly depends, on device geometries, Vdd and rise time and fall time of the input signal. Dynamic power This due to charging and discharging of the load capacitance. During each clock cycle the load capacitor charges and discharges as shown tp tp 1 2 1 P inVdd i p (Vdd Vo ) tp 0 tp tp 2 i CL dVds dt Page 7 of 12 Lecture#6 Overview tp tp 1 2 1 P CLVout dVout CL (Vdd Vo )d (Vdd Vo ) tp 0 tp tp 2 P f .CL .V 2 dd , where f is frequency of operation, Vdd is the voltage supply and CL is the load capacitance. . Total power = Pleakage + Psub-threshold +Pdynamic + Pshort-circuit Page 8 of 12 Lecture#6 Overview ARCHITECTURAL DESIGN TECHNIQUES TO REDUCE POWER CONSUMPTION Methods to reduce power consumption are many. Architectural design is one. In the following example we reduce Vdd, yet compensate for the reduction in speed and throughput with, pipelining and parallelism. A computational structure Pipelined computational structure to increase frequency of operation Parallelising the structure to increase throughput Page 9 of 12 Lecture#6 Overview Parallelising and pipelining to increase speed and throughput Assuming constant delay, ARCHITECTURE Basic Pipelined Parallel Parallel and Pipelined VOLTAGE (V) 5.0 2.9 2.9 2.0 AREA (cm2) 1.0 1.3 3.4 3.7 POWER (W) 1.00 0.39 0.36 0.20 Power is obtained by P f .CL .V 2 dd . METHODOLOGIES FOR REDUCING POWER DISSIPATION THROUGH ACTIVITY REDUCTION Usually not all subsystems are operating, thus the above model can be changed to take care of the activity. A more refined model is P a. f .CL .V 2 dd where ‘a’ is the activity factor. Page 10 of 12 Lecture#6 Overview Page 11 of 12 Lecture#6 Overview ACTIVITY OF A GATE Consider a 2-input AND gate, if we assume that the probability of input A of being at logic ‘1’ is the same as the probability of input B, which is 50%. A 0 0 1 1 B 0 1 0 1 Y 0 0 0 1 3 4 1 P1 4 P0 3 3 9 * 4 4 16 3 1 3 P01 * 4 4 16 1 3 3 P10 * 4 4 16 1 1 1 P11 * 4 4 16 P00 EXAMPLE OF ACTIVITY If PB>PA>PC, K will switch many times more uncertainty. PA 0.8 PB 0.4 PC 0.1 CONCLUSION: Always attempt to place the signal with the highest probability of switching nearer to the output or the end of the circuit. Page 12 of 12 Lecture#6 Overview