EE261 Lecture Notes (electronic)

advertisement

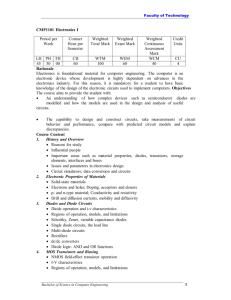

EE 261 – Introduction to Logic Circuits Module #3 - Digital Circuits • Topics A. B. C. D. E. • Digital Signaling Logic Gates Gates at the Transistor Level CMOS Static Behavior CMOS Dynamic Behavior Textbook Reading Assignments 3.1–3.6 • Practice Problems 3.1, 3.5, 3.7, 3.13, 3.27(a,c,e,g) • Graded Components of this Module 2 homeworks, 2 discussions, 1 quiz (all online) EE 261 – Introduction to Logic Circuits Module #3 Page 1 EE 261 – Introduction to Logic Circuits Module #3 - Digital Circuits • What you should be able to do after this module Draw the Symbols, Equation, and Truth Table for Basic Logic Gates Draw the transistor-level circuit of a CMOS Inverter, NAND-Gate, and NOR-Gate Describe CMOS Logic Static Behaviors (Noise Margins, Load Current, Fan-In/Out) Describe CMOS Logic Dynamic Behaviors (Delay, Power, SSN, ESD) EE 261 – Introduction to Logic Circuits Module #3 Page 2 Digital Signaling • Digital Signaling - A binary number system contains two symbols and a set of operations - But what does a '0' or a '1' look like in real life? - Many things can represents 0's and 1's, but we are interested in representing them using "electrical signals" • Logic Signals - to represent a 0 or 1, we use an electrical signal (voltage or current) - let's focus on voltage to begin with EE 261 – Introduction to Logic Circuits Module #3 Page 3 Digital Signaling • Logic Signals - a logic signal may look like this… v(t) vthreshold t - we define a threshold to represent when we consider the signal a: LOGIC 0 or LOGIC 1 EE 261 – Introduction to Logic Circuits Module #3 Page 4 Digital Signaling • Logic Signals - we say that the signal is: LOW = when the voltage is < Vthreshold HIGH = when the voltage is > Vthreshold v(t) vthreshold t Positive Logic : when a LOW represents a 0 when a HIGH represents a 1 Negative Logic : when a LOW represents a 1 when a HIGH represents a 0 EE 261 – Introduction to Logic Circuits Module #3 Page 5 Digital Signaling • Using Positive Logic v(t) vthreshold 0 1 0 1 t • Noise - Digital signals have an advantage when noise is present v(t) vthreshold 0 1 0 1 t EE 261 – Introduction to Logic Circuits Module #3 Page 6 Logic Gates • Logic Circuit - a circuit that produces logic outputs depending on the logic inputs ex) Logic • Combinational Logic - The outputs of the logic circuit depend ONLY on the current input values EE 261 – Introduction to Logic Circuits Module #3 Page 7 Logic Gates • Truth Table - a table that lists the output values for a given set of inputs in a logic circuit - for "n" inputs, there are 2n possible input combinations ex) n = 2 In1 0 0 1 1 In2 0 1 0 1 Output 0 0 1 0 - when designing a logic circuit, we typically start with the truth table EE 261 – Introduction to Logic Circuits Module #3 Page 8 Logic Gates • Logic Gates - the basic building blocks of digital logic - these represent the most simple logic operations • BUFFER Gate - Out = In 0 1 EE 261 – Introduction to Logic Circuits Module #3 Page 9 Logic Gates • NOT Gate - also called an inverter - Out = In' • AND Gate - Out = A•B = AB EE 261 – Introduction to Logic Circuits Module #3 Page 10 Logic Gates • OR Gate - Out = A + B EE 261 – Introduction to Logic Circuits Module #3 Page 11 Logic Gates • XOR Gate - Out = A B • NAND Gate - Out = (A•B)' EE 261 – Introduction to Logic Circuits Module #3 Page 12 Logic Gates • NOR Gate - Out = (A + B)' • XNOR Gate - Out = (A B )' EE 261 – Introduction to Logic Circuits Module #3 Page 13 Logic Gates • Timing Diagram - Real systems operate with respect to time - When we draw out the logic waveforms vs. time it is called a "Timing Diagram" A B Z t EE 261 – Introduction to Logic Circuits Module #3 Page 14 Logic Gates • Simple Logic Circuits - we use the basic gates to construct more complex combinational circuits - using our notation (•, +, , ') we can write the "logic expression" for complex circuits Z = (A B) + C EE 261 – Introduction to Logic Circuits Module #3 Page 15 Logic Gates • Delay - There is delay through each gate. In order to have a valid output, we must wait for the signals to propagate through all the gates in the circuit - this delay can be described using timing diagrams • Conversion to Truth Tables - From a circuit diagram, we can draw the timing diagram & truth table - From the truth table, we can draw the timing diagram & circuit diagram - From the timing diagram, we can draw the circuit diagram & truth table EE 261 – Introduction to Logic Circuits Module #3 Page 16 Gates at the Transistor Level • Logic Gates - we've seen the basic logic gates that we use to form more complex logic expressions BUF, INV, AND, NAND, OR, NOR, XOR, XNOR • Logic Signaling - we've seen how we use an electrical signal to represent and transmit logic values A 1 0 1 0 1 B 0 1 1 1 1 t EE 261 – Introduction to Logic Circuits Module #3 Page 17 Gates at the Transistor Level • Logic Families - now we want to see how we actually create these circuits and signals using electronics - there are different ways (or circuits) to implement logic gates - the circuits are designed to interface with other circuits with the same type of design - a collection of IC's designed to interface with each other is called a "Logic Family" - the most common families we deal with in school are: 1) CMOS 2) TTL EE 261 – Introduction to Logic Circuits Module #3 Page 18 Gates at the Transistor Level • MOSFET - stands for Metal Oxide Semiconductor Field Effect Transistor Drain - there are two types of MOSFET's 1) NMOS 2) PMOS Gate - this is analogous to bipolar transistors (npn, pnp) - a MOSFET is a 3 terminal device Source - this device can be thought of as a "voltage controlled resistor" - a change on the gate voltage changes the resistance between the Drain and Source - we can turn ON/OFF the flow of current by altering the voltage on the Gate EE 261 – Introduction to Logic Circuits Module #3 Page 19 Gates at the Transistor Level • NMOS D - an NMOS will allow current to flow between the Drain and Source when: IDS G VGS > 0 + VGS - When VGS = 0, no current flows S - - Cross Section of NMOS Construction Gate Source Metal Drain Oxide n n p Semiconductor EE 261 – Introduction to Logic Circuits Module #3 Page 20 Gates at the Transistor Level • PMOS VGS - a PMOS will allow current to flow between the Drain and Source when: S + IDS G VGS < 0 D - When VGS = 0, no current flows - Cross Section of PMOS Construction Gate Source Metal Drain Oxide p p n Semiconductor EE 261 – Introduction to Logic Circuits Module #3 Page 21 Gates at the Transistor Level • Basic NMOS Operation - we typically call the power supply VDD (+5v, +3.3v, +2.5v, +1.8v) - We typically call the ground either GND or VSS (0v) VDD VDD D Logic 0 D OFF G Logic 1 ON G S S GND GND EE 261 – Introduction to Logic Circuits Module #3 Page 22 Gates at the Transistor Level • Basic PMOS Operation VDD VDD S Logic 0 S ON G Logic 1 OFF G S D GND GND EE 261 – Introduction to Logic Circuits Module #3 Page 23 Gates at the Transistor Level • CMOS - we now have two complementary switches PMOS VDD VDD S S ON Logic 0 G OFF Logic 1 G S D GND GND VDD VDD D NMOS Logic 0 G D OFF Logic 1 ON G S GND S GND EE 261 – Introduction to Logic Circuits Module #3 Page 24 Gates at the Transistor Level • CMOS - CMOS = Complementary MOS - The complementary structure gives a way to always connect the output to either VDD or GND - Consider the following circuit VDD S G PMOS D Input Output D G NMOS S GND EE 261 – Introduction to Logic Circuits Module #3 Page 25 Gates at the Transistor Level • CMOS - When the Input = 0, the Output is connected to VDD VDD S G PMOS=ON D Input = 0 Output=1 D G NMOS=OFF S GND EE 261 – Introduction to Logic Circuits Module #3 Page 26 Gates at the Transistor Level • CMOS - When the Input = 1, the Output is connected to GND VDD S G PMOS=OFF D Input = 1 Output=0 D G NMOS=ON S GND - this is how we construct a CMOS Inverter EE 261 – Introduction to Logic Circuits Module #3 Page 27 Gates at the Transistor Level • CMOS Inverter - Graphically, this looks like: VDD = HIGH Vin GND = LOW Vout t EE 261 – Introduction to Logic Circuits Module #3 Page 28 Gates at the Transistor Level • MOSFET Level - we have two complementary switches VDD S Input = 0, PMOS = ON Input = 1, PMOS = OFF G S GND VDD D Input = 0, NMOS = OFF Input = 1, NMOS = ON G S GND EE 261 – Introduction to Logic Circuits Module #3 Page 29 Gates at the Transistor Level • MOSFET Level - another way to draw these is as follows: VDD S Input = 0, PMOS = ON Input = 1, PMOS = OFF G S GND VDD D Input = 0, NMOS = OFF Input = 1, NMOS = ON G S GND EE 261 – Introduction to Logic Circuits Module #3 Page 30 Gates at the Transistor Level • CMOS Gates - NMOS and PMOS transistors can be used together to form logic gates - the complementary structure is desired because the output is always being driven with a MOSFET - HIGH = a PMOS is ON and connecting the output to the VDD supply all of the NMOS's are OFF - LOW = an NMOS is ON and connecting the output to the VSS supply (GND) all of the PMOS's are OFF EE 261 – Introduction to Logic Circuits Module #3 Page 31 Gates at the Transistor Level • CMOS Inverter Input = 0 Input = 1 VDD S VDD PMOS = ON S G PMOS = OFF G S ILOAD 0 S 1 0 ILOAD 1 D D G G S S NMOS = OFF GND NMOS = ON GND EE 261 – Introduction to Logic Circuits Module #3 Page 32 Gates at the Transistor Level • CMOS NAND Gate - PMOS's in parallel provide an OR'ing structure for the connection to VDD - NMOS's in series provide an AND'ing structure for the connection to GND VDD A VDD B Output A B GND EE 261 – Introduction to Logic Circuits Module #3 Page 33 Gates at the Transistor Level • CMOS NAND Gate - We can increase the number of inputs to the NAND gate by - adding more PMOS's in parallel - adding more NMOS's in series VDD A VDD B Output A B EE 261 – Introduction to Logic Circuits Module #3 Page 34 Gates at the Transistor Level • FAN-IN - Can we increase the number of inputs infinitely? - No, because…. - adding PMOS's in parallel decreases the ON resistance and will consume too much power - the capacitance from all of the gates on a single input line will slow down the circuit - We define "Fan-In" as the number of inputs that a given device can have ex) CMOS NAND : Fan-In = 6 - the datasheet for the device will specify this EE 261 – Introduction to Logic Circuits Module #3 Page 35 Gates at the Transistor Level • CMOS NOR Gate - PMOS's in series provide an AND'ing structure for the connection to VDD - NMOS's in parallel provide an OR'ing structure for the connection to GND VDD A B Output A B GND GND EE 261 – Introduction to Logic Circuits Module #3 Page 36 Gates at the Transistor Level • CMOS NOR Gate - We can increase the number of inputs to the NOR gate by - adding more PMOS's in series - adding more NMOS's in parallel - Again, Fan-In applies A B Output A B GND EE 261 – Introduction to Logic Circuits GND Module #3 Page 37 Gates at the Transistor Level • Non-Inverting Gates - What about AND, OR, and BUF? - In CMOS, we use INV, NOR, NAND for everything - BUF Gate = 2 Inverters - AND Gate = NAND and Inverter - OR Gate = NOR and Inverter EE 261 – Introduction to Logic Circuits Module #3 Page 38 CMOS Static Behavior • Logic Levels - We need to define boundaries when the signal is considered HIGH or LOW VDD = HIGH HIGH LOW GND = LOW Vin Vout t - what is the logic level in the middle region? EE 261 – Introduction to Logic Circuits Module #3 Page 39 CMOS Static Behavior • CMOS Static Behavior - "Static" or "DC" refers to the gate's operation when the inputs are NOT changing - also called "Steady State" - if we plotted Vout vs. Vin of an Inverter, we would get… Vout Logic HIGH Logic LOW Vin EE 261 – Introduction to Logic Circuits Module #3 Page 40 CMOS Static Behavior • CMOS Static Behavior - the region in the middle is not definitely a HIGH or a LOW because of: - Power Supply Variation - Process - Noise Vout ??? Vin EE 261 – Introduction to Logic Circuits Module #3 Page 41 CMOS Static Behavior • Specification - we need to be able to guarantee operation of the gate over all possible conditions - the limits on guaranteed operation are called "specifications" - Specifications can give limits on the worst case situations - Specifications can also give limits on typical situations EE 261 – Introduction to Logic Circuits Module #3 Page 42 CMOS Static Behavior • Input Specifications VIHmin : Minimum input voltage guaranteed to be recognized as a HIGH VILmax : Maximum input voltage guaranteed to be recognized as a LOW VDD HIGH VIHmin Vin VILmax LOW VSS EE 261 – Introduction to Logic Circuits Module #3 Page 43 CMOS Static Behavior • Output Specifications VOHmin : Minimum output voltage guaranteed when driving a HIGH VOLmax : Maximum output voltage guaranteed when driving a LOW HIGH VDD VOHmin Vout LOW VOLmax VSS EE 261 – Introduction to Logic Circuits Module #3 Page 44 CMOS Static Behavior • Noise Margin HIGH State Noise Margin : (VOHmin - VIHmin) LOW State Noise Margin : (VILmax - VOLmax) Vout VDD VDD HIGH VOHmin VOLmax Vin Noise Margin Noise Margin LOW HIGH VIHmin VILmax LOW VSS VSS EE 261 – Introduction to Logic Circuits Module #3 Page 45 CMOS Static Behavior • Leakage Current - Ideally, a CMOS device driving another CMOS device will have ZERO output current - However, in reality there is a small amount of current that flows due to the implementation of the MOS's in real materials - there is a specification that tells us how much current can be expected to flow IIH : Maximum current flowing when driving a HIGH IIL : Maximum current flowing when driving a LOW EE 261 – Introduction to Logic Circuits Module #3 Page 46 CMOS Static Behavior • Resistive Loads - Sometimes we don't drive just CMOS loads - we may have resistors that are attached to the receiver - When resistors are attached, we must account for the voltage drop across the resistors when checking VILmax , VIHmin EE 261 – Introduction to Logic Circuits Module #3 Page 47 CMOS Static Behavior • Driver Models - We can model the MOSFET's as resistors - They have different resistance when they are ON (low) versus when they are OFF (high) - We can typically ignore the OFF resistance when considering the equivalent driver model - We use the driver resistance along with the load resistors to find the Input Voltages (via KVL, KCL, Ohm's Law) EE 261 – Introduction to Logic Circuits Module #3 Page 48 CMOS Static Behavior • CMOS DRIVING HIGH CMOS Driving a HIGH Equivalent Driver Model VDD S VDD PMOS = ON G Rp S ILOAD 0 ILOAD 1 D G S NMOS = OFF GND EE 261 – Introduction to Logic Circuits Module #3 Page 49 CMOS Static Behavior • CMOS DRIVING LOW CMOS Driving a LOW Equivalent Driver Model VDD S PMOS = OFF G S 1 0 ILOAD ILOAD D Rn G S NMOS = ON GND VSS EE 261 – Introduction to Logic Circuits Module #3 Page 50 CMOS Static Behavior • CMOS Resistive Loads - we need to find the voltage drop across the resistors to ensure we're meeting the input spec VDD Rp VIN > VIHmin RL EE 261 – Introduction to Logic Circuits Module #3 Page 51 CMOS Static Behavior • Load Current - there is a spec on how much current can be driven by the CMOS device - in addition to verifying that we're meeting the input voltage spec of the receiver, we must also check to see that we're not exceeding the load current spec of the driver IOH : Maximum current that can be sourced when driving a HIGH IOL : Maximum current that can be sourced when driving a LOW EE 261 – Introduction to Logic Circuits Module #3 Page 52 CMOS Static Behavior • CMOS Static Behavior - Summary of static characteristics: - Logic Levels - Noise Margin - Static DC Current - Resistive Loads - Output Current - Summary of static specifications: VIHmin VILmax : Minimum input voltage guaranteed to be recognized as a HIGH : Maximum input voltage guaranteed to be recognized as a LOW VOHmin VOLmax : Minimum output voltage guaranteed when driving a HIGH : Maximum output voltage guaranteed when driving a LOW IIH IIL : Maximum current flowing when driving a HIGH : Maximum current flowing when driving a LOW IOH IOL : Maximum current that can be sourced when driving a HIGH : Maximum current that can be sourced when driving a LOW EE 261 – Introduction to Logic Circuits Module #3 Page 53 CMOS Static Behavior • FAN-OUT - the Maximum # of devices that a gate can drive - depends on IOH and IOL - It may differ for driving HIGH vs. driving LOW (we always take the minimum #) - NOTE: We are only considering DC Fan Out EE 261 – Introduction to Logic Circuits Module #3 Page 54 CMOS Static Behavior • Datasheets - a datasheet is a document that a device manufacture provides - this lists all of the specifications for the part - the conditions for each specification are listed - we use datasheets to understand the operation of a part and whether it will work in our design EE 261 – Introduction to Logic Circuits Module #3 Page 55 CMOS Static Behavior • ESD - Electrostatic Discharge - moving objects accumulate charge - CMOS devices are very sensitive to ESD - if a large amount of ESD is discharged onto a device, it can destroy the device - the ESD has the energy to - re-diffuse doped regions - blow metal traces - fuse materials together to form a new compound - to avoid, we can: - use ESD protection circuitry within the device - discharge ourselves before touching the device EE 261 – Introduction to Logic Circuits Module #3 Page 56 CMOS Static Behavior • Latch-Up - there are parasitic bipolar transistors within the MOSFET structure (npn, pnp) - if given enough energy, these bipolar transistors can get into a positive feedback configuration and begin to conduct current through the silicon - this is a problem because a large amount of current will flow and cannot be turned off - latch up will typically burn out the IC EE 261 – Introduction to Logic Circuits Module #3 Page 57 CMOS Static Behavior • Latch-Up Prevention - at manufacturing, the npn / pnp paths are isolated from each other using guard rings EE 261 – Introduction to Logic Circuits Module #3 Page 58 CMOS Dynamic Behavior • CMOS Dynamic Behavior - We've looked at the following static characteristics: - Logic Levels - Noise Margin - Static DC Current - Resistive Loads - Output Current - Dynamic Behavior refers to when the Inputs/Outputs are switching - Also called "AC" performance - Dynamic behavior describes: 1) Speed 2) Power EE 261 – Introduction to Logic Circuits Module #3 Page 59 CMOS Dynamic Behavior • Speed - The speed of a gate depends on (i) (ii) • Transition Time Propagation Delay Transition Time - the time it takes for the Output to change between logic levels EE 261 – Introduction to Logic Circuits Module #3 Page 60 CMOS Dynamic Behavior • Speed : Transition Time - we can define the "rise time and "fall time" as the time it takes to pass through the uncertainty region Vout HIGH LOW t trise tfall EE 261 – Introduction to Logic Circuits Module #3 Page 61 CMOS Dynamic Behavior • Speed : Transition Time - transition time depends on 1) The ON Resistance of the driver 2) The capacitance of the load - for AC analysis, the DC resistance and Voltage of the load have no effect VDD - the capacitance comes from a) Output driver b) Wiring/Interconnect c) Input circuit Rp CP Cint RL CL EE 261 – Introduction to Logic Circuits Module #3 Page 62 CMOS Dynamic Behavior • Speed : Transition Time - we can model the AC circuit as one RC - the Time Constant is RC = RC VIN R VOUT C EE 261 – Introduction to Logic Circuits Module #3 Page 63 CMOS Dynamic Behavior • Speed : Transition Time Rising Edge "Exponential Approach" VOUT = VIN·(1 – e(-t/RC) ) - we assume the capacitor is NOT charged VIN R Falling Edge VOUT C "Exponential Decay" VOUT = VIN·e(-t/RC) - we assume the capacitor is fully charged - We set VIN to its steady state value at t=0 (i.e., VIN=VDD) EE 261 – Introduction to Logic Circuits Module #3 Page 64 CMOS Dynamic Behavior • Speed : Propagation Delay - the time it takes for a change on the Input to result in a change on the output - we use an inverter model for this delay where: tpLH tpHL = Δt from input falling edge to output rising edge = Δt from input rising edge to output falling edge - we use the midpoints of the transitions Vin Vout tpLH EE 261 – Introduction to Logic Circuits tpHL t Module #3 Page 65 CMOS Dynamic Behavior • Power Consumption - there are two components of power consumption 1) DC Power : when inputs are static (quiescent) - typically low in CMOS - this is also called "leakage" 2) AC Power : when outputs are switching - largest contributor to overall power (i) Short Circuit Power (ii) Load Power EE 261 – Introduction to Logic Circuits Module #3 Page 66 CMOS Dynamic Behavior • Power Consumption - Short Circuit Power - at the moment of time when an output is half way through its transition, both the PMOS and NMOS are on. VDD - this creates a path from VDD to GND S PSC = PT = CPD · VDD · f PMOS = ON G S VDD/2 - CPD is the "Power Dissipation Capacitance" (given by MFN) D ISC G S NMOS = ON GND EE 261 – Introduction to Logic Circuits Module #3 Page 67 CMOS Dynamic Behavior • Power Consumption - Load Power - the power is takes to charge & discharge the load capacitance PL = CL · VDD2 · f VDD - CL is the sum of all load capacitance S PMOS = ON G (driver + interconnect + receiver) S D CL IL G NMOS = OFF S GND EE 261 – Introduction to Logic Circuits Module #3 Page 68 CMOS Dynamic Behavior • Power Consumption - Total Power PD = (CPD + CL) · VDD2 · f VDD S PMOS = ON - CL tends to dominate G S D CL IL ISC G NMOS = OFF S GND EE 261 – Introduction to Logic Circuits Module #3 Page 69 CMOS Dynamic Behavior • Simultaneous Switching Noise (SSN) - What happens when we switch logic levels with a capacitive load? VDD S PMOS = ON G S D CL IL G NMOS = OFF S GND - the capacitor looks like a short at AC (or when transitioning) EE 261 – Introduction to Logic Circuits Module #3 Page 70 CMOS Dynamic Behavior • Simultaneous Switching Noise (SSN) - this causes a large instantaneous current to be drawn from the power supply - the power supply cannot supply this sudden change in current because it has a much slower response - we can think of the power supply as a large capacitor that stores our charge. The interconnect that supplies this charge to our device tends to be inductive and resistive. - when we draw current quickly through the interconnect, there is voltage drop - as a result, the power supply voltage will begin to "droop" as seen by our device EE 261 – Introduction to Logic Circuits Module #3 Page 71 CMOS Dynamic Behavior • Simultaneous Switching Noise (SSN) - "Decoupling Capacitors" - we can put decoupling (or bypass) capacitors near our device to provide the faster, instantaneous current draw due to switching logic levels. VDD R,L CDecoupling S PMOS = ON G S D CL IL G NMOS = OFF S GND EE 261 – Introduction to Logic Circuits Module #3 Page 72 CMOS Dynamic Behavior • Simultaneous Switching Noise (SSN) - "Ground Bounce" VDD - when the interconnect on the IC is inductive, we will get a voltage drop when instantaneous current is drawn. + VL - L VL = L (di/dt) - this causes the VDD (or GND) on-chip to be different from the VDD (or GND) in the system. S PMOS = ON G - this is called "Ground Bounce" S - this leads to inadvertent switching of logic circuits - this problem becomes more sever when multiple signals share the same VDD or GND pin D CL IL G NMOS = OFF S GND EE 261 – Introduction to Logic Circuits Module #3 Page 73 Module Overview • Topics - Truth Tables - Logic Gates - Simple Logic Circuits - Timing Diagrams - MOSFETS - NMOS, PMOS, CMOS - CMOS Inverter - CMOS NAND - CMOS NOR - CMOS AND,OR,BUF - CMOS Static Behavior - Input Specs - Output Specs - Noise Margin - Leakage - Resistive Loads - Fan-In / Fan-Out - Latch-Up - CMOS Dynamic Behavior - transition time / propagation delay - power consumption (SC & Load) - Decoupling - Ground Bounce / SSN EE 261 – Introduction to Logic Circuits Module #3 Page 74