Project #

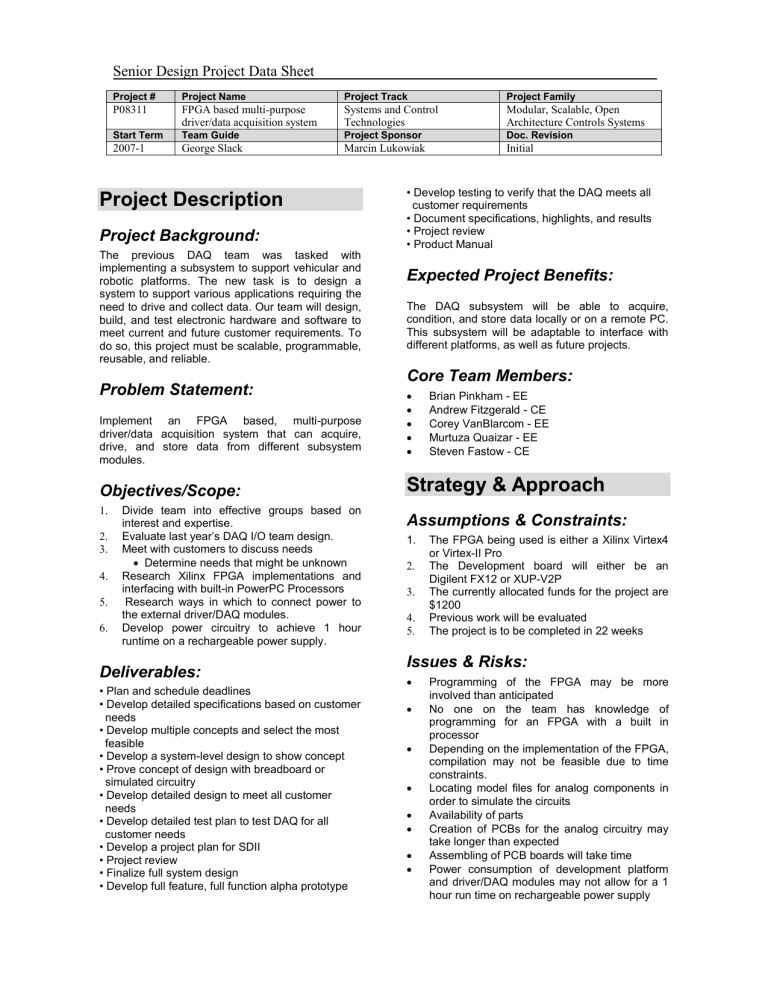

Senior Design Project Data Sheet

Project #

P08311

Project Name

FPGA based multi-purpose driver/data acquisition system

Start Term Team Guide

2007-1 George Slack

Project Track

Systems and Control

Technologies

Project Sponsor

Marcin Lukowiak

Project Description

Project Background:

The previous DAQ team was tasked with implementing a subsystem to support vehicular and robotic platforms. The new task is to design a system to support various applications requiring the need to drive and collect data. Our team will design, build, and test electronic hardware and software to meet current and future customer requirements. To do so, this project must be scalable, programmable, reusable, and reliable.

Problem Statement:

Implement an FPGA based, multi-purpose driver/data acquisition system that can acquire, drive, and store data from different subsystem modules.

Objectives/Scope:

1.

Divide team into effective groups based on interest and expertise.

2.

Evaluate las t year’s DAQ I/O team design.

3.

Meet with customers to discuss needs

Determine needs that might be unknown

4.

Research Xilinx FPGA implementations and interfacing with built-in PowerPC Processors

5.

Research ways in which to connect power to the external driver/DAQ modules.

6.

Develop power circuitry to achieve 1 hour runtime on a rechargeable power supply.

Deliverables:

• Plan and schedule deadlines

• Develop detailed specifications based on customer needs

• Develop multiple concepts and select the most feasible

• Develop a system-level design to show concept

• Prove concept of design with breadboard or simulated circuitry

• Develop detailed design to meet all customer needs

• Develop detailed test plan to test DAQ for all customer needs

• Develop a project plan for SDII

• Project review

• Finalize full system design

• Develop full feature, full function alpha prototype

Project Family

Modular, Scalable, Open

Architecture Controls Systems

Doc. Revision

Initial

• Develop testing to verify that the DAQ meets all customer requirements

• Document specifications, highlights, and results

• Project review

• Product Manual

Expected Project Benefits:

The DAQ subsystem will be able to acquire, condition, and store data locally or on a remote PC.

This subsystem will be adaptable to interface with different platforms, as well as future projects.

Core Team Members:

Brian Pinkham - EE

Andrew Fitzgerald - CE

Corey VanBlarcom - EE

Murtuza Quaizar - EE

Steven Fastow - CE

Strategy & Approach

Assumptions & Constraints:

1. The FPGA being used is either a Xilinx Virtex4 or Virtex-II Pro

2.

The Development board will either be an

Digilent FX12 or XUP-V2P

3.

The currently allocated funds for the project are

$1200

4.

Previous work will be evaluated

5.

The project is to be completed in 22 weeks

Issues & Risks:

Programming of the FPGA may be more involved than anticipated

No one on the team has knowledge of programming for an FPGA with a built in processor

Depending on the implementation of the FPGA, compilation may not be feasible due to time constraints.

Locating model files for analog components in order to simulate the circuits

Availability of parts

Creation of PCBs for the analog circuitry may take longer than expected

Assembling of PCB boards will take time

Power consumption of development platform and driver/DAQ modules may not allow for a 1 hour run time on rechargeable power supply