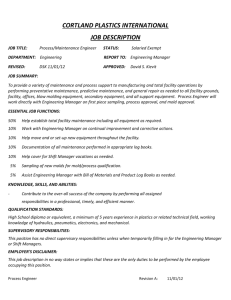

experience - Legacy Engineering

advertisement

Legacy Engineering, LLC 18662 MacArthur Blvd. Suite 457 Irvine, CA 92612-1426 Telephone: (949) 794-5860 Home Page: www.Legacyeng.com JOHN J. BOLLINGER OBJECTIVE I am interested in assignments where I can apply my 40+ years of experience in digital design, logic synthesis and simulation methods, mixed analog/digital circuit design, test and system integration, system design, test and integration. EXPERIENCE 02/2004 to Present: Legacy Engineering, LLC, Irvine, CA 01/2011 to Present: Consultant. Assigned to Boeing Company as Electric Design and Analysis Engineer. 07/2005 to 06/2008: Consultant. Assigned to Boeing Company as a Contract Engineer. Designed and constructed test equipment for the ordnance and valve driver circuitry of the Navy SM3 missile program 02/2004 to 2005: Consultant. Assigned to DRS Technologies as Contract Engineer. Supported for Mast Mounted Sight (“MMS”) production resolving production problems on circuit cards/box assemblies. Led design efforts to upgrade the MMS processor box reducing the card count from 15 to 2 circuit cards. 10/2002 to 2/2004: DRS Technologies, Cypress, CA Lead Engineer. Supported MMS electro-optic system production operations. Resolved production problems on circuit cards and box assemblies, redesigned circuit cards as parts became obsolete, and supported units fielded with the Army. 10/1996 to 10/2002: Boeing Company, Anaheim, CA IPT Lead Engineer. Designed, fabricated, assembled, tested and integrated an Infra Red Focal Plane Array test set. Test set required innovative high-speed digital (>100 MHz) technology and fabrication methods. Worked as the IR&D IPT defining ‘next generation’ processor communication hardware architecture involving Fiber Channel technology. Responsible for the design of three hardware modules, checkout, system integration and financial management (> $1M) of the Guidance Electronic Set for the Navy SM3 anti-missile system (IR sensor kinetic kill weapon, TI C31 processor with a XILINX 4025E FPGA for all I/O functions). 06/1971 to 10/1996: Rockwell DEO, Anaheim, CA 04/1995 to 10/1996: Team Leader. Led team for the digital electronics portion of the GPS IIF satellite program. Managed the conceptual design, completed project JOHN J. BOLLINGER Page 2 EXPERIENCE (CONTINUED) planning and participated in the proposal preparation for GPS IIF bid. Managed staffing, detailed design and sub-contractor performance after contract award as the NDU team leader. Developed expertise with Microsoft Project as the project planning tool for GPS IIF. 10/1994 to 04/1995: Lead Engineer. Designed, fabricated and integrated the PAC3 (RADAR sensor missile interceptor) Digital Processor Factory and Engineering test equipment. Worked on test programming with LABVIEW software. 07/1993 to 10/1994: Lead Engineer. Designed and simulated of 4 Xilinx 4000 FPGA’s for the M-MIGITS program (GPS-aided guided weapon). The FPGA’s provided input/output interface with internal RAM to a C31 processor. Capture and simulation were done in Viewlogic’s CAE environment utilizing X-BLOX elements, Register Transfer Language (“RTL”) and schematic input. 01/1992 to 07/1993: Lead Engineer. Worked with Rockwell’s SPPD TMS320C30based signal processor. Directed the efforts of three engineers in completing the design, simulation, layout, fabrication and test of a new SPPD-based processor (4 C30’S) for a hover-vehicle demonstration (Advanced Kinetic Vehicle). This project was completed start to finish in 3 months with first build success of the PCB (20 layer PCB with surface mounted components on two sides). Completed the design, simulation and layout of hover vehicle electronics for the Navy LEAP program. 03/1991 to 01/1992: Lead Engineer. Completed the system integration of a VMEbased Dual Band Radar Processor for the Target Acquisition for Ship Defense (“TASD”) program consisting of three VME chassis with 54 VME cards total. 01/1990 to 03/1991: Lead Engineer. Performed the conceptual system design and the top-level digital design of a data collection system for the MTAS Radar system, consisting of a VME chassis with 16 cards (an 80486 embedded VME processor, five dual ported VME memory cards and five special design input data processing cards). Worked on the Airborne Self Protective Jammer program (Digital RF Memory – “DRFM”) modified and debugged HP basic software for the HP9000 series 300 computer-based digital system test station and verified DRFM hardware performance. 10/1988 to 01/1990: Lead Engineer. Performed the conceptual system design and the top-level digital design of a VME-based Dual Band Radar Processor for the TASD program consisting of three VME chassis with 54 VME cards total. Directed the efforts of six engineers and technicians. 12/1982 to 09/1988: Lead Engineer. Directed the efforts of two engineers in resolving production start-up problems on the Digital Scan Converter (“DSC”) system (converted the analog output of a linear array of 120 horizontally-scanned infrared sensors into digital words and processed the scene data for display on a RS-170 video monitor). Integrated the Digital Scan Converter system into a Tank Thermal Site (“TTS”) for use as the Infrared Imaging Data Acquisition system (“IIDAS”). Tasks involved the full spectrum of system development from design, fabrication, test, noise reduction (2 micro volt signal levels) and calibration to field integration and support. JOHN J. BOLLINGER Page 3 EXPERIENCE (CONTINUED) 09/1976 to 12/1982: Digital Engineer. Application engineer for the Rockwell V96P/1 modem. Worked closely with customers to integrate the modem into their products at lowest cost and greatest added value. Helped to secure several large contracts for this modem. Designed, built and debugged an adaptive data rate controller for unattended operation of the V96P/1 modem. Presented seminars at WESCON Convention (Summer 1981) on the theory and operation of the V96P/1 modem. Modified four complex ASIC devices using RTL synthesis, simulation and layout required to upgrade the Rockwell-produced Codex 9600 BPS modem to the new international communications standards. 01/1973 to 09/1976: Electronic Engineer. Participated in the system design using RTL synthesis, layout, simulation, fabrication and checkout of the MISAR engine control computer developed for General Motors to control the ignition advance on the 1978 Oldsmobile Tornado (the first microprocessor to be used in a production automobile). 06/1971 to 01/1973: Electronic Engineer. Designed ASIC devices for PPS-4 based cash register machines using RTL synthesis, layout and simulation. Designed I/O for a digital automotive fuel injection computer and supported field trials of this unit. 02/1968 to 06/1970: Hughes Aircraft Company, Newport Beach, CA Technician/Engineer. Microelectronics. EDUCATION B.S.E.E. – California State University, Long Beach, CA CLEARANCES Secret