The LOC project status and SMU's plan in ASICs - Indico

advertisement

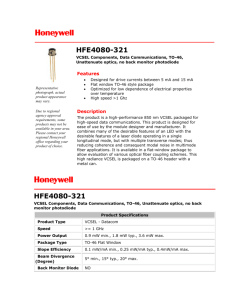

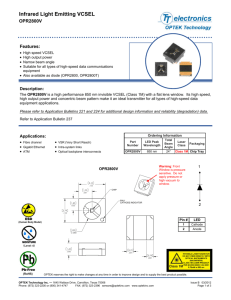

The LOC project status and SMU’s plan in ASICs Jingbo Ye for the LOC project at SMU The project is actually lead by Datao Gong For details on recent LOC results please see this talk at TWEPP: hIps://indico.cern.ch/contribuLonDisplay.py?sessionId=17&contribId=164&confId=228972 There are two developments: § The dual channel serializer: ü LOCs2: 2×8 Gb/s 16:1 serializer, prototype, tested to design goals. o LOCx2: 2×5.12 Gb/s 8:1 serializer for ATLAS LAr phase-­‐1, low latency, low power, with framing, CRC, and scrambling. In design. Will be QFN-­‐88 packaged. Transmits any 12-­‐bit serial output ADC data. § The VCSEL drivers: ü LOCld1: 8 Gb/s VCSEL driver with I2C, QFN-­‐24, tested to design goals. This is a generic VCSEL driver with SLVS inputs. With VCSEL at 8 Gbps < 200 mW. • ? LOCld4: 4-­‐ch open-­‐drain array VCSEL driver. Tested but with problems. o LOCld2: 2-­‐ch TOSA VCSEL driver for MTx. Submission: Dec. 2013. o LOCld8: 8-­‐ch array VCSEL driver, try to fix problems idenLfied with LOCld4. submission Dec. 2013. Future plans: § serializer: • • Follow the SOS technology (PC process, 180 nm) to move to 10 Gb/s per channel. Join CERN for 65 nm development. § VCSEL drivers: • • • Probe the speed of open-­‐drain array VCSEL driver with the current GC process. LOCld12: 12-­‐ch array VCSEL driver to complete the LOCld4,8, and 12 series. Join CERN for 65 nm development. Backup slides LOCs2 design features Serializing unit 4 2:1 Mux 8 4:2 Mux 8:4 Mux 16 16:8 Mux LVDS Rec 16 Data 2 SerialData @ 8Gbps CML Driver Clock Dividers LC VCO LPF Dn Charge pump PFD Up Div2 Div2 Div2 LVDS Rec 500 MHz Clock PLL Serializing unit Clock Dividers 2 2:1 Mux 4 4:2 Mux 8 8:4 Mux 16 16:8 Mux 16 LVDS Rec Data CML Driver SerialData @ 8Gbps • Two (2) channel 16:1 serializer sharing one LCPLL; Each channel operates at 8 Gbps. • LVDS 16-­‐bit × 2 data and 500 MHz clock inputs. • Input data can be latched with either edges of the internal clock. • Output CML signal > 200 mV over a 100 ohm differenLal load. • LC-­‐tank PLL with loop bandwidth programmable from 1.3 to 6.8 MHz. • Power consumpLon 1.2 WaI. 5 Wire-­‐bonded LOCs2 LOCs2 test setup • The LOCs2 die is wire-­‐bonded to a PCB. A QFN packaged version will be tested soon. • Input PRBS 27-­‐1 data from the LOCs2 tested together with LOCld1 Kintex-­‐7 board; Output serialized data to high-­‐speed oscilloscope for jiIer and eye measurement. 6 LOCs2 eye diagrams 100 mV/div. 8 Gbps 8.48 Gbps • LOCs2 works from 6.6 to 8.5 Gbps, limited by the LCPLL tuning range . • Measured power consumpLon is 1.25 waI at 8 Gbps, matching simulaLon. 7 LOCs2 bathtub curve • The bathtub curve of LOCs2 at 8 Gbps. • At 10-­‐12 the eye has an opening of about 60 ps. 8 LOCs2 jiIer performance 30 1 28 1.1 0.95 27 1 0.9 Random ji+er (ps) Total ji+er (ps) 26 25 24 23 Channel A 22 Channel B 21 Random ji+er (ps) 1.2 29 0.9 0.8 Channel A 0.7 Channel B 0.6 7 7.5 8 Data rate (Gbps) 8.5 9 0.8 0.75 0.7 0.65 0.5 20 0.85 7 7.5 8 8.5 Data rate (Gbps) 9 0.6 400 Icp =40 uA, loop bd = 2MHz Icp = 80uA, loop bd = 2.2 MHz 450 500 550 Reference clock (MHz) • Measure jiIer with a 50 Gs/s real Lme oscilloscope. • Measure the total jiIer (pk-­‐pk) of the serial output bit stream to be about 30 ps with the input PRBS 27-­‐1 parallel data. RJ about 1 ps. • Measure the PLL jiIer through a clock signal divided-­‐by-­‐8 from the VCO clock; Only random jiIer is significant in this case and it is measured to be below 1 ps. 9 LOCld1 design VDD V33 Vctrl M5 Vcom R1 M6 M3 R4 R3 M4 Vout_p Vout_n R2 Vin_p M1 M2 M7 M8 Vin_n Pre-drive 2 Pre-drive 1 V25 I2C bus Iref Iref Voltage DAC Vctrl I2C Iref Main drive Ibias Iref Ibias_ref Iref Current DAC Ibias_ref Pre-drive 6 LOCld1 • 8-­‐Gbps single channel VCSEL driver with acLve shunt peaking. • I2C slave and DAC module (thanks to Sandro Bonacini and Paulo Moreira) for remote configuraLon. • Programmable: VCSEL bias and modulaLon currents; peaking strength. • VCSEL bias and modulaLon currents refer to a constant current source, not sensiLve to transistor threshold voltage change caused by radiaLon. 10 LOCld1 lab test LOCld1 test board I2C master • LOCld1 is wire-­‐bonded to a PCB for this test. A QFN-­‐24 packaged version will be tested soon. • Input 200 mV PRBS signal from signal generator and from LOCs2. • Output signal to oscilloscope through SMA connectors for electrical test, to a VCSEL for opLcal signal test. • VCSEL modulaLon current programmable (4 bits) up to 7.6 mA. VCSEL bias current programmable (4 bits) up to 8 mA. 11 LOCld1 eye-­‐diagrams RJ = 0.89 ps DJ = 11.7 ps TJ = 21.8 ps 5 Gbps 9 Gbps RJ = 0.9 ps DJ = 15.5 ps TJ = 26.0 ps 8 Gbps 10 Gbps 12 LOCld1 irradiaLon tests LOCld1 test board Test system LOCld1 test board in X-­‐ray chamber LOCld1 has been verified to meet ATLAS LAr front-­‐end electronics TID requirement. LOCld1 has also been tested in a neutron beam of 800 MeV. No bit error is found in the data transmission, and in its I2C configuraLon circuit. 13 LOCld4 design innerVCSEL Peaking Vctrl Vin_p Vin_p Vin_p Vin_n Vin_p Vin_n Vin_n Vin_n Five amplifier stages Five amplifier stages Five amplifier stages Five amplifier stages out in Tail current reference LOCld4 Biasing Biasing current Biasing Output stage current Biasing Output stage current Output stage current Output stage Bias V control • 4-­‐channel 8 Gbps VCSEL array driver, taken advantage of one submission with spare design area in one corner. • Design: acLve shunt peaking + open-­‐drain last stage • Design VCSEL modulaLon current 6 mA 14 LOCld4 lab test preliminary • • • • Input: Diff 200mV (peak-­‐peak) at 5Gbps Output: Bias-­‐Tee PE1606 (100k ~ 12.4GHz) pulling up to 3.3V 5 Gbps eye-­‐diagram looks good, but amplitude is only 200 mV Problem idenLfied, next design to be submiIed in Dec. 2013 15 LOCx2 dedicated to ATLAS LAr • • • • LOCx2 is a 2-­‐channel full funcLonal 5.12 Gbps transmiIer for ATLAS LAr trigger upgrade in phase I. LOCx2 interfaces to 8 channel 12 or 16 bits ADC serial outputs with the full digital block LOCic. LOCic and the new LCPLL will be submiIed December 2013. LOCx2 is planned to be packaged in QFN-­‐88 (10 mm × 10 mm). 16 LOCic design • • • • • Simi-­‐manual layout based on foundry’s digital library plus a pipeline technique are used to research the speed of 640 MHz. The design is opLmized to reduce transmission latency (to transmit trigger data ) and overhead. 12-­‐bit BCID is encoded in the data frame. CRC-­‐8 code is added to detect transmission error; Scrambler is included to transfer DC-­‐ balanced data. Design is in final checking stage. 17 LOCic design LOCic layout 18 LC-­‐PLL for LOCx2 LC_PLL 40 MHz SLVS Receiver Up PFD Dn Charge pump LC-­‐Tank VCO LPF 2.56 GHz 40 MHz Div by 32 2.56 GHz To Serializer 1.28 GHz Diff to CMOS 1.28 GHz CML Divider by 2 1.28 GHz 40 MHz/640 MHz Outputs • • LVDS Drivers 40 MHz With phase ctrl 640 MHz Dividers with phase control SCL SDA I2C Controller 32-­‐b 2.56 GHz LC-­‐tank PLL with 2.56 GHz and phase adjustable 640 MHz and 40 MHz clock outputs. The Input reference clock is 40 MHz; Loop bandwidth is programmable from 500 KHz to 2 MHz 19 LC-­‐PLL for LOCx2 LCPLL layout 20 LOCs2 and LOCld1 package • 10 dies of LOCld1v2 are packaged in 5mm x 5mm 24-­‐pin QFN. • 10 dies of LOCs2 are packaged in 12mm x 12mm 100-­‐pin QFN. • The test boards of packaged chips are ready for test (Put packaged chip photo here) LOCld1 with 24-­‐pin QFN LOCs2 with 100-­‐pin QFN 21