IE_F10_lecture10

advertisement

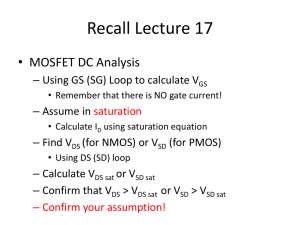

Lecture 10 Metal-Oxide-Semiconductor (MOS) Field-Effect Transistors (FET) MOSFET Bias Analysis Goals • Investigate circuits that bias transistors into different operating regions. • • • • Two Supplies Biasing Four Resistor Biasing Two Resistor Biasing Biasing using Current Mirror • Understand Bias Point Stability • Investigate DC Analysis for P-Channel Transistor Bias Analysis Approach • Assume an operation region (generally the saturation region) • Use circuit analysis to find VGS • Use VGS to calculate ID, and ID to find VDS • Check validity of operation region assumptions • Change assumptions and analyze again if required. NOTE :An enhancement-mode device with VDS = VGS is always in saturation Bias Analysis of n-channel MOSFET Check VGS we start the analysis by assuming certain operating region VGS> Vt VGS< VTN VDS < VGS –VTN Triode region Cutoff region iD=0 iD 1 2 K n '( W L )[ 2 (V GS V TN )V DS ] VDS > VGS –VTN Sat. region iD 1 2 K '( W L )( V GS V TN ) 2 Example-1 Biasing using two voltage supplies for gate and drain terminal Example 2 ( Biasing in Triode Region) Also V I DD D (R D R ) V S DS 4 1600 I V DS V D DS 2 . 19 V But VDS<VGS-VTN. Hence, saturation region assumption is incorrect Using triode region equation, Assumption: IG=IB=0, transistor is saturated (since VDS= VGS) Analysis: VGS=VDD=4 V I D 250 μA ( 4 1) 2 1 . 13 mA 2 V2 V μA 250 4 V 1600 ( 4 1 DS )V DS DS 2 V2 2 V DS 2 . 3V and ID=1.06 mA VDS<VGS-VTN, transistor is in triode region Q-pt:(1.06 mA, 2.3 V) Four-Resistor and Two-Resistor Biasing • Provide excellent bias for transistors in discrete circuits. • Stabilize bias point with respect to device parameter and temperature variations using negative feedback. • Use single voltage source to supply both gate-bias voltage and drain current. • Generally used to bias transistors in saturation region. • Two-resistor biasing uses lesser components that fourresistor biasing and also isolates drain and gate terminals Bias Analysis: Example3 (Four-Resistor Biasing) Assumption: Transistor is saturated, IG=IB=0 Analysis: First, simplify circuit, split VDD into two equal-valued sources and apply Thevenin transformation to find VEQ and REQ for gate-bias voltage Problem: Find Q-pt (ID, VDS) Approach: Assume operation region, find Q-point, check to see if result is consistent with operation region Bias Analysis: Example 3 (Four-Resistor Biasing) (contd.) V GS V 2 0 . 05V GS GS 7 . 21 0 2 . 71 V , 2 . 66 V Since VGS<VTN for VGS= -2.71 V and MOSFET will be cut-off, V Since IG=0, V EQ 4 V V GS GS 25 V K R n S 2 10 EQ V V GS 6 GS V 3 . 9 10 2 I TN R D S 2 4 V GS 1 2 GS 2 . 66 V and ID= 34.4 mA I Also, V V 6 . 08 V DS DD D (R D R ) V S DS VDS>VGS-VTN. Hence saturation region assumption is correct. Q-pt: (34.4 mA, 6.08 V) with VGS= 2.66 V Two Resistor Biasing Biasing the MOSFET using a large drain-to-gate feedback resistance, RG. VDD> Vt MOS is ON and always in saturation (diode connected transistor) V D VG V DS V GS iD 1 2 K ' (W / L )( V DS V t ) V DS V dd i D R D 2 Bias Analysis: Example 4 (Two-Resistor Biasing) V GS V V GS DD 3 .3 V K R n D 2 2 . 6 10 V GS V 4 10 2 4 2 GS TN V GS 1 0 . 769 V , 2 . 00 V Since VGS<VTN for VGS= -0.769 V and MOSFET will be cut-off, Assumption: IG=IB=0, transistor is saturated (since VDS= VGS) Analysis: V DS V DD I R D D V GS 2 . 00 V and ID= 130 mA VDS>VGS-VTN. Hence saturation region assumption is correct. Q-pt: (130 mA, 2.00 V) 2 Additional Biasing Circuits_2 Using constant current source iD iS I I 1 2 ( K ' W / L )( V GS V t ) 2 V GS V G V S , V G 0 I 1 2 Vs ( K ' W / L )( V S V t ) 2I K 'W / L Vt 2 How to implement a current source (Current mirrors) For Q1 For Q2 V DS V GS diode connected I ref I D 1 V GS 1 V t 1 2 transisto r K ' W / L (V GS 1 V t ) 2 2 I D1 .......... .........( 1) V GS 2 V GS 1 2 I DS 2 K ' (W / L ) 2 K 'W / L I DS 2 V DS 1 V GS 1 V DD I ref R .......... ..( 2 ) (W / L ) 2 I ref is given 2 I DS 1 K ' (W / L ) 1 I ref (W / L ) 1 N-branch current mirror I1 I2 (W/L)1 (W/L)2 Iref In W/L Iref (W / L ) I1 (W / L ) 1 I2 (W / L ) 2 (W/L)n In (W / L ) n n-channel and P-Channel MOSFETs DC –Analysis of P-channel MOS Note: The direction of current is out of the drain for a PMOS Bias Analysis: Example 5 (Two-Resistor biasing for PMOS Transistor) Also 15 V ( 220 kΩ ) I 15 V ( 220 kΩ ) V GS D V DS 0 2 50 μA V 2 0 V GS 2 V 2 GS 0 . 369 V , 3 . 45 V Since VGS= -0.369 V is less than VTP= -2 V, VGS = -3.45 V Assumption: IG=IB=0, transistor is saturated (since VDS= VGS) Analysis: V GS ( 470 kΩ ) I G V DS 0 ID = 52.5 mA and VGS = -3.45 V V DS V GS V TP Hence saturation assumption is correct. Q-pt: (52.5 mA, -3.45 V) Example The circuit below uses a p-channel enhancement MOSFET with k’(W/L) = 2 mA/V2 and Vt = -1 V. Find the value for R that produces V0 = 10 V. Modifications to Drain Current Equations Channel-Length Modulation Increasing vDS beyond vDSsat causes the channel pinch-off point to move slightly away from the drain, thus reducing the effective channel length (by ΔL). Effect of vDS on iD in the saturation region. The MOSFET parameter VA depends on the process technology and, for a given process, is proportional to the channel length L. It can be called; channel length modulation (λ), or Early voltage (VA) Example • A saturated MOSFET is operated with a constant vGS. The drain current, iD, is found to be 2 mA for vDS = 4 V and 2.2 mA for vDS = 8 V. Find the values of VA, λ and ro. Including the effect of Channel Length Modulation in the MOSFET model (Valid in the Saturation region) iD ro 1 K '( W 2 1 I D L )( V GS V t ) (1 V DS ) VA 2 Output resistance ID W 1 2 ro K ' ( )( V GS V t ) L 2 1 Bias-Point Stability for MOS Amplifiers (source degeneration) iD iD Variations in K’(W/L) VG Rs RS Rs VGS=VG-iDRS Large Rs stable bias point but requires large supply voltage Rs is called degeneration resistance VGS Vt1 Vt2 Variation in Vt