On-die L2

advertisement

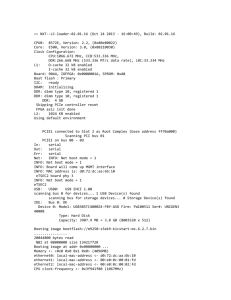

10. Rendszerarchitektúrák Busses: Figure 1.: Busses Figure 2.: Main features of the system-bus Figure 3.: General purpose peripheral busses Figure 4.: Early implementations of the ISA-bus Figure 5.. Dedicated busses Figure 6.: Storage interfaces Figure 7.: IDE/ATA Figure 8.: Basic transfer modes of the IDE/ATA standards Figure 9.: SCSI Figure 10.: AGP Figure 11.: AC ’97 Figure 12.: AC ’97 Figure 13.: Implementation of the AC ’97 DRAMs: Figure 14.: DRAMs Figure 15.: Memory modules Figure 16.: Serial Presence Detect (SPD) Figure 17.: Packaging of memory modules Figure 18.: DIMMs Figure 19.: The JEDEC Serial Presence Direct (SPD) standard for DIMMs Figure 20.: PC100 module identification CHIPSETS: Figure 21.: Overview of the Intel chipsets Figure 22.: Chipsets I.: Supported DRAM features Figure 23.: Chipsets II.: Supported I/O-features Figure 9.4: Main features of Intel’s 845xx family of chipsets Figure 9.10: Intel’s chipsets designed for P4-based value and desktop PCs Figure 9.14: Bus innovations introduced into Intel’s P4 chipsets Figure 9.16: The evolution of chipsets intended primarily for P4-based value/mainstream desktops Table 9.30: Main features of the FSB and SDRAM interface Table 9.31: Main features of MCH/ICH interfaces of Intel’s P4-based chipsets Table 9.32: Main features of high speed MCH interfaces of Intel’s P4-based chipsets Table 9.33: Peak bandwidth values and sustained data rates of peripheral buses Figure 9.34: Peak bandwidth values (Mbyte/s) in a typical value/desktop motherboard based on Intel’s 865xx family of chipsets Figure 9.35: Peak bandwidth values (Mbyte/s) in a typical value/desktop motherboard based on Intel’s 915xx family of chipsets System architecture: Figure 24.: Evolution of the system architecture Figure 25.: ISA-bus based system architecture (Used typically in 08088/80286/80386-based PCs) Figure 26.: Straight forward PCI-based system architecture (Used typically in 486 and early Pentium-based PCs along with Intel 420 and early 430 chipsets) Figure 27.: PCI-based system architecture with IDE/ATA and USB ports (Used typically in mature Pentium-based PCs with mature Intel 430 chipsets) Figure 28.: PCI-based system architecture with AGP, IDE/ATA and USB ports(Used typically in early PentiumII and PentiumIII-based PCs with Intel 440XX chipsets) Figure 29.: Ports-based system architecture (Used typically in mature PentiumIIand PentiumIII-based systems with Intel 8X0 chipsets Excluding the 810, which includes an integrated display controller rather than an AGP port) Figure 30.:Mainstream evolution of the system architecture Caches: Figure 31.: Evolution of cache architectures Figure 32.: Main features of AMD K6 and Athlon K7 cores Figure 33.: Main features of Intel’s Pentium II/III and Pentium 4 cores Figure 34.: Main parameters of L1 caches Figure 35.: - External L1-cache - On-die unified L1-cache with optional (external, unified) L2-cache - On-die split L1-cache with optional (external, unified) L2-cache - Direct coupled L2-cache - On-die L2-cache - On-die L2-cache with an external front-end L3-cache - On-die L2-cache with a direct coupled L3-cache Busses System bus (Host bus) (Processor bus) General purpose peripheral bus Figure 1.: Busses Dedicated busses Main features of the system-bus Width of the 8086 8088 address bus (bit) 20 1 20 1 24 32 data bus (bit) 16 1 81 16 32 80286 1 Multiplexed 2 Bits 0,1 not implemented (Doubleword aligned) 3 Bits 0-2 not implemented (Quadword aligned) 4 For error protection 80386 2 80486 32 32 2 Pentium 32 3 64 Figure 2.: Main features of the system-bus Pentium Pro PII PIII P4 36 36 36 36 64+8 4 64+8 4 64+8 4 64+8 4 General purpose periphe ral busses ISA (Industry Standard Architecture) 1984: IBM PC/AT bus The bus of the PC/AT became a de facto standard. The term ISA was coined later. EISA (Extenced ISA) MCA (Microchannel Architecture) 1987: IBM 1988: A number of companies led by Compaq The proprietary bus of the IBM PS/2 line of PCs. (This line was intended to cope with the clone-makers of the PC-line.) VESA VL (Video Electronics Standard Association, (VESA) Local Bus) 1992: Version 1. VESA An extension to the ISA bus, An alternative to IBM's MCA. 16-bit/8 MHz (2 cycles/B) 32-bit/8 MHz 32-bit/8.33 MHz 8 MB/s 32 MB/s 33 MB/s PCI (Peripheral Component Interchange Bus) 1992: Version 1. Intel 2 The PCI specification was developed by Intel as an alterative to the VESA VL standard. 32-bit Performance, trend 1 It originates from the IBM PC-bus which appeared in 1981 (8-bit wide, 4.77MHz) 2 Now managed by the PCI Special Interest Group Consortium. Figure 3.: General purpose peripheral busses Vers. 1.: 32-bit/33 MHz Vers. 1.: 132 MB/s Processor type 8088 80286 80386 20-bit 24-bit 24-bit 8-bit 16-bit 32-bit 4,77 MHz 6/8 MHz 20-bit 24-bit 8-bit 16-bit freqency 4,77 MHz 6/8 MHz pin-count 62 62+36 Processor bus address width data width freqency 16/25/33 MHz ISA bus address width data width 8 MHz Figure 4.: Early implementations of the ISA-bus Dedicated busses Storage i.f. (HD, CD-ROM, tape back-up etc.) IDE/ATA SCSI Video i.f. AGP Audio i.f. AC'97 RS-232 Figure 5.. Dedicated busses Low speed peripheral bus USB X-bus LPC GPIB Storage interfaces (Hard disk interfaces) ST-506/ST-412 IDE*/ATA (Integrated Device Electronics) SCSI (Small Computer System Interface) (AT - Attachment) Seagate Technologies Separate drive and controller Now it is obsolete 1981: Westen, compaq, CDC The controller is integrated on the drive. Less expensive, desktop systems use ATA. 1986: Shugart, NCR The controller is integrated on the drive. More expensive (10-25%). In servers/workstations/ tape backup systems. They are expected to offer highter performance as SCSI devices can exchange data without the intervention of the host processor. Serial Parallel, 16/32-bit Parallel, 8/16-bit 0.625 MB/s 8-133 MB/s 5-160 MB/s * The term IDE was coined in 1986. Figure 6.: Storage interfaces IDE/ATA ATA Fast ATA EIDE ATA-2 ATA-3 2 ATA-4* ATA-5 * 3 (1991) (withdrawn in 1999) (1994) (~1994) (1996) (withdrawn in 2001) (1997) (1998) (2000) Seagate Western Digital Small Form Factor Committee CAM Committee (from a group of companies) ANSI X3-221-1994 X3-279-1996 CHS-addressing (Cylinder, Head, Sector) max. 504 MB* 1 pair of drives (1 channel) Logical Block addressing 1 NCITS 317-1998 NCITS 340-2000 ATAPI (ATA Packet Interface) for additional support of CD-ROMs, tape drives etc. Logical Block addressing 137.5 GB 16 M-TeraB 2 pair of drives (2 channels) 32-bit(?) 16-bit 4.17 MHz 8.3 MB/s 16 MB/s 6.67 MHz 8.33 MHz 13.3 MB/s 16.7 MB/s Performance, trend *1 *2 3 * *4 (under development) Technical Committee TI3 of NCITS X3-298-1997 Additional support of Based on Fast ATA CD-ROMs, tape drives etc. and EIDE ATA-6 * 4 The addressable disk capacity is restricted by both the ATA and the BIOS addressing schemes. The synchronous DMA, Mode 2 of ATA-4 is called ATA/33. The synchronous DMA, Mode 4 of ATA-5 is called ATA/66. The synchronous DMA, Mode 4 of ATA-6 is called ATA/133. Figure 7.: IDE/ATA 8.33 MHz (double clocked) 33.3 MB/s 16.67 MHz (double clocked) 66.6 MB/s 16.67 MHz (double clocked) 133.3 MB/s Basic transfer modes of the IDE/ATA standards PIO Programmed I/O Mode 0 - Mode 5 Single Word DMA Transfer of one word at a time Mode 0 - Mode 2 Multiple Word DMA Burst mode DMA transfer Mode 0 - Mode 2 Figure 8.: Basic transfer modes of the IDE/ATA standards Synchronous DMA Double clocked burst mode DMA transfer Mode 0 - Mode 4 SCSI SCSI-1 SCSI-2 (1986) (1991) SCSI-3 (In 2001 not yet formally approved, but it is considered to be the current standard) SCSI T10 Committee Wiring standards 1 GB 8-bit 5 MHz SPI P1394 SSA (SCSI Parallel Interface) Firewire (100 MB/s serial) System Storage Architecture 8 GB 8-bit/16-bit 5 MHz/10 MHz FC-AL (Fibre ChannelArbitrated Loop) 8-bit/16-bit 20 MHz/40 MHz (Fast SCSI) (Ultra SCSI)/(Ultra2 SCSI) SPI SCSI-2 Plain Fast Wide Fast Wide Ultra Ultra Wide Ultra 2 Ultra 2 Wide Data width 8-bit 8-bit 16-bit 16-bit 8-bit 16-bit 8-bit 16-bit 8-bit 16-bit Bus frequency 5 MHz 10 MHz 5 MHz 10 MHz 20 MHz 20 MHz 40 MHz 40 MHz 40 MHz 40 MHz Transfer rate 5 MB/s 10 MB/s 10 MB/s 20 MB/s 20 MB/s 40 MB/s 40 MB/s 80 MB/s 80 MB/s 160 MB/s Performance, trend Figure 9.: SCSI Ultra 80/m Ultra 160/m Wide AGP The principle of the AGP port Processor bus Graphic chip Memory bridge (North bridge) Frame buffer I/O bridge (South bridge) Main memory AGP (Intel) (PCI) Clock speed Bus Version 1.0 Version 2.0 (7/1998) (Based on Revision 2.1 of the PCI) (5/1998) 66 MHz (Multiplexed 32-bit address bus /data bus) (Transfer of 4-byte data blocks) Seperate 32-bit address bus and 32-bit data bus Transfer of 8-byte data blocks Transfer mode 1x (AGP-66) 2x (AGP-133) (double clocked) 4x (AGP-266) (quadruple clocked) Transfer rate 264 MB/s 532 MB/s 1064 MB/s Figure 10.: AGP AC '97 (Audio Codec) Traditional sound solution: ISA/PCI bus KBD SP Sound card Mouse PP Analog audio input/output (mono, stereo sound, mic etc.) Principle of the AC '97 solution: Separation of the primarily digital and analog parts, designated as Digital Controller (DC) and Analog Codec (AC), as shown below. These parts are connected via a 5 wire digital interface, called the AC '97 Link. AC '97 Digital Controller AC '97 Link (5 wire digital) AC '97 Analog Codec The original AC '97 interface description specifies the functionality of the AC '97 Analog Codec and defines a 5 wire digital link (AC '97 Link) to the AC '97 Digital Controller. Figure 11.: AC ’97 AC '97 Version 1.0 Version 2.0 Revision 2.1 Revision 2.2 6/1996: 5 vendors (Intel, ADI, Creative Labs, National Semiconductor, Yamaha). (9/1997) (5/1998) (9/2000) Link: 5-wire digital (2 serial data lines) Audio Codec 16-bit optionally 18/20-bit AD/DA resolution 48 KHz sampling rate 4 analog stereo inputs 2 analog mono inputs 4/6 channel output dedicated mic input Digital controller High Quality audio (up to 96 KHz sampling rate 120 dB dynamic range) Modem extension (Cost effective) Multiple codec capability (for multichannel audio solutions etc.) May reside on any bus (ISA, PCI, USB, 1394) or in an I/O-bridge Figure 12.: AC ’97 Implementation of the AC '97 AC '97 Digital Controller ISA /USB/ 1394 AC '97 Digital Controller AC '97 Link Analog audio inputs/ outputs AC '97 Analog Codec AC '97 Link I/O-bridge (South Bridge) AC '97 Dig. Contr. AC '97 Codec AC '97 Link Motherboard Usually implemented as part of the South Bridge Figure 13.: Implementation of the AC ’97 AC '97 Link Motherboard DRAM 1 FPM 2 EDO3 BEDO4 SDRAM 5 DRDRAM 6 Since 1996 Asynchronous Synchronous Burst mode access (4*8B) on the same row (page) Up to 66 MHz bus frequency 66/100/133 MHz Random access, typ. access time 60/70/80/100 ns Access to 4 subsequent columns (60 ns) ~ 40 ns ~ 25 ns (5-5-5-5) (5-7)-3-3-3 (5-7)-4-4-4 (5-7)-2-2-2 5-1-1-1 (5-7)-1-1-1 Max. bandwidth MB/s Effective bandwidth MB/s Triton III.: 7-1-1-1 430 ZX.: 7-1-1-1 820 840 Developed by RAMBUS Cycle time within a burst (for a 60 ns part) Full burst timing Examples Overlapping the read and address transfer operations Internal 2-bit address generator, dual banks ~ 15 ns Triton I.: 7-3-3-3 Triton I.: 7-2-2-2 Triton III.: 6-3-3-3 Triton II,III.:6-2-2-2 Internal on-chip Full pipelined operation, SRAM cache, assuming at least page is filled in dual banks 1 clock cycle,1-2 B wide data path 256/300/356/400 MHz transfer rate ~ 15/10/7.5 ns Developed by MICRON Remakes (4/3.3/2.8/2.5 ns) Level of overlapping Cached structure 1 Dynamic RAM 2 Fast Page Mode DRAM 3 Extended Data Out DRAM 4 Burst mode EDO Synchronous DRAM 6 Direct Rambus DRAM 5 Figure 14.: DRAMs Memory modules (FPM/EDO/SRDRAM) 1-byte wide modules (8-bits) 30-pin SIPP 30-pin SIMM 4-byte wide modules (32/36-bits) 8-byte wide modules (64/72-bits) 72-pin SIMM (FPM/EDO) 168-bit DIMM Unbuffered FPM/EDO DRAM Storage capacity (MB) 1/16-16 PPD on some implementations 386 Presence Detect Typical use in systems based on Unbuffered SDRAM Registered SDRAM 8-512 2-512 SPD SPD SPD PPro (mostly FPM) PII (only EDO) PII/PIII PIII 1-2048 PPD 486 Pentium PPro Trend PPD: Parallel Presence Detect: Memory parameters and features can be accessed in parallel from a built in EEPROM SPD: Serial Presence Detect: Memory parameters and attributes may be serilly accessed from a built in EEPROM. Figure 15.: Memory modules Serial Presence Detect (SPD) ~ 40 memory parameters held in an SPD-EEPROM (2-kbit) Byte 2: Memory type 02H: EDO 04H: SDRAM Byte 9: Cycle time in tenths of ns e.g. 75H: 7.5 ns (for PC133) Further data: - Memory capacity - Access time - CAS-latency After switching on, the BIOS reads the data from the EEPROM, and the memory controller part of the chipset will be set accordingly. Figure 16.: Serial Presence Detect (SPD) Packaging of memory modules SIMM DIMM SIPP Single In-line Pin Package Module Single In-line Memory Module Dual In-line Memory Module A single row of pin connectors, Twin rows of edge connectors Twin rows of independent designed for soldering in place. with opposite connectors edge connectors RIMM Rambus In-line Memory Module Dedicated DIMM developed for Rambus memory connected together so each pair of connectors provides 30-pins (8-bit wide memory modules) the same contact. Usually 30/72 pins 168 pins (8- or 32-bit wide memory modules) (64-bit wide memory modules) Trend Figure 17.: Packaging of memory modules 184 pins (16-bit wide memory modules) DIMMs 72-bit SO DIMMs (Small Outline DIMM) 144-bit SO DIMMs (Small Outline DIMM) 168-bit DIMMs Designed for portables Designed for portables Designed for desktops/workstations/servers 32/36-bit wide memory module 64/72-bit wide memory module 64/72-bit wide memory module Typical for SDRAMs, but early implementations include FPM or EDO DRAMs, as well. Unbuffered Registered (buffered) Unbuffered SDRAMs can drive a smaller number of memory chips Buffered SDRAMs can drive a larger number of memory chips Figure 18.: DIMMs The JEDEC Serial Presence Detect (SPD) standard for DIMMs. Recent implementations support PC100 PC133 SDRAMs SDRAMs (Intel's PC100 standard (1997) VIA's PC133 standard (1999) JEDEC's registered PC100 SDRAM JEDEC's registered PC133 SDRAM) Module identification (Intel, VIA) PC100 requires 8 ns parts, PC133 needes 7.5 ns parts. Figure 19.: The JEDEC Serial Presence Direct (SPD) standard for DIMMs PC100 module identification (according to Intel) PCX-abc-def X: Clock frequency (MHz) For PC100 modules 100 a: CAS-latency in cycles Typically 2-3 cycles b: RAS-CAS-delay in cycles Typically 2-3 cycles c: RAS-precharge-time in cycles Typically 2-3 cycles d: Output valid in ns (Access time) Maximum 6 ns e: SPD-revision nr., last digit E.g. for revision 1.2: 2 f: Reserved, now 0. E.g. PC100-322-610 CAS-latency: The time between appearing the column address (CAS-signal) and appearing the data RAS-CAS-latency: The time between the RAS and CAS signals RAS-precharge time: Before a new RAS signal is allowed to appear Latency for accessing a new row: RAS-prechange + RAS-CAS-latency + CAS-latency Latency for accessing new colums on the same page: CAS-latency RAS: Row Address Strobe CAS: Column Address Strobe Figure 20.: PC100 module identification Overview of the Intel chipsets 420 family 430 family 486-based Pentium-based 440 family Pentium II/III-based (early chipsets) 450 family Pentium Pro-based (mostly) Pentium II/III-based (more recent chipsets) 800 family Figure 21.: Overview of the Intel chipsets Servers/Workstations 1993 Type 1995 450 KX Mars P PPro Target 2 Nr. of CPUs Proc. bus fr. (MHz) DRAM 1/2 1 FPM P ECC SIMM/72 SIMM/72 DIMM(u) 430 HX Trion II Febr. PPro 4 2 FPM 1996 450 GX Orion 60/66 60/66 max. size (GB) type FPM DRAM EDO DRAM SDRAM RDRAM Error prot. Sockets 1994 430 NX Neptune June 60/66 2 60/66 4 1/2 FPM EDO ECC SIMM/72 DIMM(u) PPro/PII P FPM ECC SIMM/72 1997 440 LX 440 FX Natoma May? Aug April PII PII/PIII 2 2 60/66 66 1 1-1/2 FPM EDO EDO 1999 820 Camino Nov. PIII 2000 440 GX 450 NX PII Xeon/ PIII Xeon PII Xeon/ PIII Xeon 4 2 2 100 100 100/133 133 2 8 1/4-1/2-1 2 2 2 66/100 1 EDO SDRAM SDRAM EDO SDRAM SDRAM SDRAM SDRAM ECC ECC ECC ECC DIMM(u) DIMM(u/r) DIMM DIMM ECC SIMM/72 DIMM(u) 1998 440 BX 840 Carmel PIII/ PIII Xeon EDO EDO RDRAM RDRAM RDRAM RDRAM RIMM RIMM RIMM RIMM opt. ECC ECC Desktops 1993 Type Target Nr. of CPUs Proc. bus fr. (MHz) DRAM max. size (MB) type FPM DRAM EDO DRAM SDRAM RDRAM Error prot. Sockets 1994 430 LX Mercury 1995 430 FX Triton Febr. P 1 60/60 192 FPM P SIMM/72 SIMM/72 P 1 50/60/66 128 1996 430 VX Triton III. Febr. P 1 50/55/60/66 128 1997 1998 430 TX 440 EX Jan. March. P PII (Cel.) 1 1 60/66 66 256 256 440 ZX PII 1 66/100 440 MX Mobile PII/ PII Cel. 1999 810 Whitney June? PII(Cel.)/ PIII Cel. 2000 815 850 PII(Cel.) PIII P4 1 1 1 66/100 66/100 100/133 256 512 2048 FPM EDO SDRAM FPM EDO SDRAM EDO SDRAM EDO SDRAM SDRAM SDRAM SDRAM - P - - - - - SIMM/72 SIMM/72 DIMM SIMM/72 1 DIMM (u) - DIMM(u/r) DIMM(u/r) DIMM(u) DIMM(u) FPM EDO DIMM(u/r) 1 100 RDRAM opt. ECC RIMM 1 For FPM/EDO: 72-pin SIMM/144-pin SO-DIMM for SDRAM: 168-pin DIMM/144-pin SO-DIMM Figure 22.: Chipsets I.: Supported DRAM features u: Unbuffered SDRAM r: Registered (buffered) SDRAM Identifies related or derived chip sets Servers/workstations 1993 Type 1994 1995 430 NX Neptune June 450 KX Mars 2 2 Nr. of CPUs Target P PPro PCI AGP ATA USB AC'97 1.0 2.0 LPC Nr. of chips 4/5 (VESA/EISA) 1996 450 GX Orion 4 8 430 HX Trion II Febr. 2 1997 440 LX 440 FX Natoma May? Aug 2 2 PPro P PPro/PII 2.0 2.1 2.1 Y Y 2.1 2x ATA/33 Y 3 Y 2 12 2 PII 440 BX 1998 440 GX April 2 2 PII Xeon/ PIII Xeon 2.1 2x ATA/33 Y PII/PIII 2.1 2x ATA 33/66 Y Y 2 450 NX 4 PII Xeon/ PIII Xeon 2.1 ATA/33 Y Y 6 1999 820 Camino Nov. 2000 840 2 2 PIII PIII/ PIII Xeon 2.2 4x ATA/66 Y 1.0 Y 3 2.2 4x ATA/66 Y 1.0 Y 3 Desktop 1993 1994 1995 1996 1997 1998 430 VX Triton III. Febr. 1 430 TX 440 EX 1 430 FX Triton Febr. 1 Jan. 1 March. 1 Target P P P P PII (Cel.) PCI AGP ATA USB AC'97 1.0 - 2.0 - 2.1 Y 2.1 2x ATA/33 ATA/33 Y Y 2.1 2x ATA/33 ATA/33 Y Y 4/5 (VESA/EISA) 4 4 2 2 Type Nr. of CPUs 430 LX Mercury 440 ZX 1 PII 2.1 2x ATA/33 Y 440 MX 1 Mobile PII/ PII Cel. 2.2 ATA/33 Y 1.1 1.0 LPC Nr. of chips Figure 23.: Chipsets II.: Supported I/O-features 1 1999 810 Whitney June? 1 PII(Cel.)/ PIII Cel. 2.2 ATA 33/66 Y 1.0 Y 3 2000 815 850 June 1 1 PII(Cel.) P4 PIII 2.2 2.2 4x 4x ATA33/66/100 ATA33/66/100 Y Y 2.1 2.1 Y Y 3 3 845xx family Features MCH/GMCH Memory (Brookdale) Single channel SDR/DDR SDRAM (unbuffered) 2 GB1 Max. memory FSB HT support DRAM speed PC133 9/01 Memory protection 400 MHz 533/400 MHz HT not supported HT supported PC133, DDR 266/200 12/01 845 845 ECC (opt.) ECC (opt.) Integrated graphics (IG) Graphics interface up to ICH PC133, DDR 266/200 PC133, DDR 266/200 5/02 5/02 5/02 845G 845E 845GL AGP 4X ICH2: ICH2: IG AGP 4X ICH4: ICH4: ICH4: PCI 2.2 10/100 Mbit/s Target core at introduction 1 2 DDR 333/266 DDR 333/266 10/02 10/02 845GE 845PE IG AGP 4X AGP 8X ICH4: ICH4: ICH4: USB 2.0 Ultra ATA/100 LAN Target line at introduction 845GV AGP 4X PCI AC '97 10/02 IG ATA up to USB DDR 266/200 ECC (opt.) IG AGP 4X DDR 266/200 2 USB 1.1 USB 1.1 USB 2.0 USB 2.0 USB 2.0 USB 2.0 USB 2.0 AC '97 2.1 AC '97 2.1 AC '97 2.3 AC '97 2.3 AC '97 2.3 AC '97 2.3 AC '97 2.3 AC '97 2.3 P4 P4 Celeron P4 P4 Celeron/P4 P4 P4 Willamette Northwood-A Willamette-128 PGA 478 PGA 478 PGA 478 Northwood-B without HT Northwood-128/ Northwood-B with HT Northwood-B with HT PGA 478 The 845 has a max. memory of 2 GB for DDR SDRAMs and 3 GB for SDR SDRAMs. At introduction of the 845G and 845E chipsets (5/02) Intel did not made any notice about supporting hyperthreading. But in 10/02 Intel revealed that the enhanced 845G (B stepping) and the original 845E do support hyperthreading with upgraded BIOSs. Figure 9.4: Main features of Intel’s 845xx family of chipsets 11/00 Core s FSB Willame tte 400 MHz 8/01 1/02 Willame tte 400 MHz Northwood-A 400 MHz 11/02 5/03 2/04 Northwood-B 5/02 Northwood-B Northwood-C Pre scott 533 MHz 533 MHz 800 MHz 800 MHz HT HT HT HT 6/04 Pre scott F 800 MHz 800 MHz HT HT LGA 775 EM64T LGA 775 EM64T Socket PGA 423 PGA 478 9/01 Chipse ts 11/01 845 PGA 478 PGA 478 5/02 845G/E PGA 478 PGA 478 10/02 5/03 865P PGA 478 8/03 845GV/GE/PE 848P 5/03 9/03 5/03 865G/GV/PE 4/03 875P 6/04 9/03 6/04 915G/GV/P Figure 9.10: Intel’s chipsets designed for P4-based value and desktop PCs 8/04 Pre scott 11/02 AGP 8x AGP 5/03 SATA 1.0a SATA 5/03 PC I 2.3 PC I 2/04 PC I-X 2.2 PC I-X 6/04 PC I Expre ss PC I Expre ss 1.0a 5/02 USB USB 2.0 12/01 AC ' 97 AC ' 97 2.3 6/04 HDAI HDAI 2001 2002 2003 2004 Figure 9.14: Bus innovations introduced into Intel’s P4 chipsets P4 FSB VGA AGP 4X/8X/PCI Express x.16 1 2 MCH (845/845xx/848P/865xx/ 875P/915xx) SDRAM interface SDRAM 3 interface Max. 2/4 GB 4 PC 133, DDR 200/266/333/400, DDR2 400/533 SDRAM unbuffered, ECC opt. 3 SDRAM HI 1.5/DMI ICH2 ICH4 ICH5(R) 6x v2.2 6x v2.2 6x v2.3 5 ICH6(R) 7x v2.3 6 ICH2 PCI ATA/100 PCI-X 4 4x v1.1 6x v2.0 8x v2.0 8x v2.0 v2.1 v2.3 v2.3 v2.3 PCI Express x1 845xx 848P 865xx 875P 915xx 2 2 2 2 SATA ICH ICH5(R) 5 ICH6(R) 6 46 LAN 10/100 GPI0 AC/97 5 ICH2/4/5/5R /6/6R 6 LPC FWH 845 845xx 848P 865xx 875P BIOS 1 The chipsets including the letter G in their designation provide an integrated graphics controller. 2 The chipsets including the letters GL or GV in their designation don't have an AGP or PCI Express x16 interface. 3 The 845, 845xx and 848P chipsets have a single channel memory link, while the others listed above have a dual channel link. The 845 has a max. memory of 3 GB for SDR SDRAMs. 5 The ICH5R includes an integrated RAID controller that utilizes the dual SATA ports for a high performance RAID Level 0 implementation. 4 6 1 5 USB HDAI 845 ICH4 The ICH6R includes an integrated RAID controller that utilizes the dual SATA ports for a high performance RAID Level 0 implementation. Figure 9.16: The evolution of chipsets intended primarily for P4-based value/mainstream desktops 915xx Width Peak aggregate bandwidth FSB 64-bit 8 * f c Mbyte/s SDRAM-interface 64-bit 8 * f SDRAM Mbyte/s Table 9.30: Main features of the FSB and SDRAM interface Used in the chipsets Width Peak aggregate bandwidth HI 1.5 All prior chipsets 8-bit 266 MByte/s DMI 910GL, 915xx, 925X, 925XE 4*1 bit 2000 MByte/s Table 9.31: Main features of MCH/ICH interfaces of Intel’s P4-based chipsets Used in the chipsets HI CSA HI 2.0 PCI E. x8 Width Peak aggregate bandwidth 16-bit 533 MByte/s 8-bit 266 MByte/s E7500/7501/7505 16-bit 1066 MByte/s E7221/7320/7520/7525 8*1 bit 4000 MByte/s 860 848P/865xx/875P/E7210 Table 9.32: Main features of high speed MCH interfaces of Intel’s P4-based chipsets Peak bandwidth MByte/s AGP 4X 1066 AGP 8X 2132 VGA port Sustained data rate up to MByte/s analog port MbE c. 12.5 GbE c. 125 SCSI Ultra 320 320 Ultra ATA/100 100 ~30-60/drive SATA 1.0 150 ~30-60/drive PCI 32-bit/33 MHz 133 PCI-X 64-bit/66 MHz 533 PCI-X 64-bit/133 MHz 1066 PCI E. x1 500 PCI E. x4 2000 PCI E. x8 4000 PCI E. x16 8000 USB 1.0 ~125 60-90/drive, ~200-250/bus ~400-450 1.5 USB 2.0 60 AC'97 ~1.4 HDA 3/SDI, 6/SDO LPC ~5 ~50 Table 9.33: Peak bandwidth values and sustained data rates of peripheral buses P4 Northwood B/C FSB 400/533/800 MHz 2132 AGP 8x 865xx1 VGA GbE GbE c. 3200-6400 CSA (HI 1.5) (GMCH) 266 HI 1.5 MbE c. MbE PCI v.2.3 ICH5 CODEC AC'97 v.2.3 SDRAM 21323200 SDRAM interface SDRAM 4 GB DDR 266/333/400 unbuffered, no ECC Ultra ATA/100 (2 ports) 2*100 USB 2.0 (6-8 ports) Audio SDRAM interface 266 133 PCI v.2.3 (3 slots) 21323200 SATA (2 ports) 2*150 GPIO 1.4 ~5 LPC SIO FWH FD KB MS SP PP Figure 9.34: Peak bandwidth values (Mbyte/s) in a typical value/desktop motherboard based on Intel’s 865xx family of chipsets P4 Prescott FSB 533/800 MHz PCI E. x16 VGA PCI E. x16 PCI E. x16 8000 915xx 1 (G)MCH 8000 DMI MbE c. MbE PCI v.2.3 (2-4 slots) GbE Audio GbE c. PCI v.2.3 PCI E. x1 SDRAM interface SDRAM 26644264 SDRAM interface SDRAM 4 GB DDR 333/400, DDR2 400/533 unbuffered, no ECC 2000 1*100 Ultra ATA/100 (1 ports) 4*150 SATA (4 ports) 500 ICH6 500 USB 2.0 (8 ports) 60 AC'97 v.2.3 26644264 133 PCI E. x1 (1-2 ports) CODEC 3200-6400 1.4 GPIO ~5 LPC SIO FWH FD KB MS SP PP Figure 9.35: Peak bandwidth values (Mbyte/s) in a typical value/desktop motherboard based on Intel’s 915xx family of chipsets System architecture ISA-based PCI-based With IDE/ATA and With AGP, IDE/ATA USB-ports and USB-ports 486 and early Pentium-based PCs Mature Pentium-based PCs Early PII and PIII-based PCs Mature PII/PIII-based PCs Intel 420 early 430 chipsets Mature Intel 430 chipsets Intel 440XX Intel 8X0 chipsets chipsets Straightforward 8088/80286/ 80386-based PCs Port-based Trend Figure 24.: Evolution of the system architecture 8088/80286/80386 Processor Memory/ Bus controller KBD Main Memory (DRAM/FPM) ISA Monitor Adapter WD Adapter FD Adapter PP Adapter SP Adapter Multi-I/O card I/O devices Figure 25.: ISA-bus based system architecture (Used typically in 8088/80286/80386-based PCs) 486/Pentium Processor bus L2 cache System controller Main Memory (FPM/EDO) PCI bus Peripheral controller PCI device adapter ISA bus ISA device adapter (Legacy and/or slow devices) Figure 26.: Straight forward PCI-based system architecture (Used typically in 486 and early Pentium-based PCs along with Intel 420 and early 430 chipsets) Pentium Processor bus L2 cache System controller Main Memory (FPM/EDO/SDRAM) PCI bus IDE/(ATA/33) USB Peripheral controller PCI device adapter ISA bus ISA device adapter (Legacy and/or slow devices) Figure 27.: PCI-based system architecture with IDE/ATA and USB ports (Used typically in mature Pentium-based PCs with mature Intel 430 chipsets) IDE port: First on the 430FX (Triton, 1995) ATA/33: First on the 430TX (1997) USB: First on the 430VX (Triton III, 1996) PentiumII/ PentiumII/ PentiumIII PentiumIII Processor bus AGP System controller Main Memory (EDO/SDRAM) PCI bus 2xIDE/ATA33/66 Peripheral controller PCI device adapter (Legacy and/or slow devices) 2xUSB ISA bus ISA device adapter Figure 28.: PCI-based system architecture with AGP, IDE/ATA and USB ports (Used typically in early PentiumII and PentiumIII-based PCs with Intel 440XX chipsets) PentiumII/ PentiumIII Processor bus AGP System controller Main Memory (SDRAM/RDRAM) Hub interface LPC 2xIDE/ ATA 33/66/100 Peripheral controller 2x/4x USB Super I/O (KBD, MS, FD, SP, PP, IR) AC'97 PCI bus PCI to ISA bridge PCI device adapter ISA bus ISA device adapter (Legacy and/or slow devices) Figure 29.: Ports-based system architecture (Used typically in mature PentiumII- and PentiumIII-based systems with Intel 8X0 chipsets Excluding the 810, which includes an integrated display controller rather than an AGP port) ISA General purpose peripheral buses PCI SCSI IDE/ATA AGP Dedicated I/O-ports AC'97 LPC 1980 81 82 83 84 85 86 87 88 89 1990 91 General purpose peripheral buses 92 93 94 95 96 97 98 99 2000 01 Dedicated I/O-ports Figure 30.: Mainstream evolution of the system architecture Caches Added feature External (unified) L1 L1 External Unified On-die L1 Split L1 External (unified) L2 Direct coupled L2 On-die L2 External (unified) L3 Direct coupled L3 On-die Split On-die External L2 Direct coupled Direct coupled Unified External L3 Direct coupled Unified Intel x/86 386 (opt.) 486 1 Pentium Pentium (opt.) PPro PII (except Mendocino) PIII (0.25 μ) PII (Mendocino) PII/PIII (0.18 μ) P4 IA/32 (P4 orig.design) Itanium IA/64 AMD Kx K5 K6 K6-2 K5 (opt.) K6 (opt.) K6-2 (opt.) Athlon (K7, K75 cores) Trend 1 Optionally extended with on external, unified L2 cache Figure 31.: Evolution of cache architectures K6-2+ Athlon (Thunderbird core) Athlon 4 Duron (Spitfire core) K6-III K6-III+ Server/Workstation models (Athlon MP-line) Performance desktop models (K6/Athlon-line) 4/97 Δ K6 Model 6 (0.35 μ/8.8 mtrs) 166/200/233 MHz Opt. L2 through FSB Socket 7 1 5/98 Δ K6-2 (0.25 μ/9.3 mtrs) 266/300/333 MHz Opt. L2 through FSB Socket 7 1 1/98 Δ K6 Model 7 (0.25 μ) 266/300 MHz Opt. L2 through FSB Socket 7 1 8/99 6/00 Δ Δ Athlon K7 Thunderbird (0.25 μ/22 mtrs) (0.18 μ/37 mtrs) 500/550/600/650 MHz 750-1000 MHz Direct coupled half speed L2 On-die full speed L2 3 (512 KB) (256 KB) Slot A Socket-A 11/99 3/99 Slot-A (OEMs only) Δ Δ Athlon K75 K6-III (0.18 μ/22 mtrs) (0.25 μ/21.3 mtrs) 750 MHz 400/450 MHz Ext. 0.4 times 2 On-die full speed L2 core speed L2 (256 KB) (512 KB) Socket 7 1 Slot A 6/01 Δ Model 6 (0.18 μ) 1/1.2 GHz On-die full speed L2 (256 KB) Socket A 6/01 Δ Athlon 4 (0.18 μ/37.5 mtrs) 1.4-1.5 GHz 3 On-die full speed L2 (256 KB) Socket-A 6/00 Δ Spitfire (0.18 μ/25 mtrs) 600/650/700 MHz On-die full speed L2 (64 KB) Socket-A Low-end desktop models (Duron-line) 1997 1998 (MMX supported) 1 Actually 321 pin CPGA (Ceramic Pin Grid Array) 2 Later, higher speed versions (900/950/1 GHz) used 1/3 speed L2 3 Exclusive L2 1999 (3D-Now! supported) 2000 (Enhanced 3D-Now! supported) 2001 (3D-Now! Professional supported) (~SSE) mtrs: Million transistors FSB: Front-side Bus Slot-A: Mechanically identical to Slot 1 but it is electriclly different Socket A (Socket 462): Physically the same as the Socket 7 or the Socket-370 Figure 32.: Main features of AMD K6 and Athlon K7 cores 1/99 10/99 6/98 5/00 Δ Δ Δ Δ Tanner Cascades Cascades Xeon (0.25 μ) (0.25 μ) (0.18 μ) (0.18 μ) 400 M Hz 500 M Hz 700 M Hz 600/667/700 M Hz Ext. full-speed L2 Ext. full-speed L2 On-die full-speed L2 On-die full-speed L2 (0,5/1 M B) (0,5/1/2 M B) (1/2 M B) (0.25 M B) Slot2 Slot2 Slot2 Slot2 S erver/Workstation models (Xeon-line) Performance desktop models 11/95 Δ Pentium Pro (0.6 μ/0.35 μ/5.5 mtrs) 150/180/200 M Hz Ext. full-speed L2 (256 K) Socket8 5/97 Δ Klamath (0.28 μ/7.5 mtrs) 233/266/300 M Hz Ext. half-speed L2 (512 KB) Slot1 1/98 Δ Deschutes (0.25 μ) 333 M Hz Ext. half-speed L2 (512 KB) Slot1 2/99 Δ Katmai (0.25 μ/8.5 mtrs) 450/500 M Hz Ext. half-speed L2 (512 KB) Slot1 Low-end desktop models (Celeron-line) 3/00 Δ Coppermine128 (0.18 μ/28.1 mtrs) 566/600 M Hz On-die full-speed L2 (128 KB) FC-PGA 8/98 Δ Mendocino (0.25 μ/19 mtrs) 300/333 M Hz On-die full-speed L2 (128 KB) Slot1 1995 1996 Pentium Pro (M M X added) Slot1: SECC 242 Slot2: SECC 330 SECC: Single Edge Contact Connector Socket8: 387-pin PGA 1997 1998 Pentium II (M M X added) FC-PGA: Flip Chip Pin Grid Array Ext.: External direct coupled mtrs: M illion transistors Figure 33.: Main features of Intel’s Pentium II/III and Pentium 4 cores 11/00 Δ Pentium 4 (0.18 μ/42 mtrs) 1.4/1.5 GHz On-die full speed L2 (256 KB) 423-pin PGA 10/99 Δ Coppermine (0.18 μ/28.1 mtrs) 500-733 M Hz On-die full-speed L2 (256 KB) Slot1/FC-PGA1 4/98 Δ Covington (0.25 μ) 266 M Hz No ext. L2 Slot1 5/01 Δ Xeon 1.7 GHz (0.18 μ/42 mtrs) 1.4/1.5/1.7 GHz On-die full speed L2 (0.25 M B) 603-pin micro PGA 1999 2000 2001 Pentium 4 (SSE2 added) Pentium III (SSE added) 1 Only the 500/550 M Hz models L1 instruction cache Bytes per cache line 4-way Nonblocking 8 KB 2-way WB/WT Y 8 KB 2-way 16 KB Y 16 KB Y 16 KB Y 16 KB Y Y 8 KB 16 KB Y 16 KB 32 KB Y 32 KB Y K6-2 32 KB Y 32 KB Y K6-3 32 KB Y 32 KB Y K7 64 KB Y 64 KB Y Thunderbird 64 KB 2-way Y L: 3 clocks 64 KB 2-way Y Athlon 4 64 KB 2-way Y 64 KB 2-way Y 1 8 KB Bytes per cache line Organization 16 B Organization Nonblocking Size Intel 486 Size L1 data cache Pentium 32 B 8 KB 2-way PPro 32 B 8 KB 4-way PII PIII P4 Itanium AMD K6 32 B Trace cache (12 K μops) 1 Unified instruction/data cache 2 No FP data stored Figure 34.: Main parameters of L1 caches 4-way 2 Y Y Y Processor Bus interface unit Processor bus L1-cache System Contr. Memory Core Logic External L1-cache Examples: Intel 386 based systems with optional L1-cache L1-cache Processor Bus interface unit Processor bus L2 Cache System Contr. Memory Chipset (core logic) On-die unified L1-cache with optional (external, unified) L2-cache Examples: Intel 486-based systems D-cache I-cache Processor Bus interface unit Processor bus L2 Cache System System Contr. Contr. Memory Chipset On-die split L1-cache with optional (external, unified) L2-cache Exmples: Intel Pentium, AMD K5, K6, K6-2 based systems Processor D-cache I-cache L2 Cache Bus interface unit Processor bus System Contr. Memory Chipset Direct coupled L2-cache Examples: Intel Pentium Pro, Pentium II (expect Mendocino), Pentium III (0.25μ technology) and AMD Athlon (K7, K75 cores) based systems D-cache I-cache L2-cache Processor Bus interface unit Processor bus System Contr. Memory On-die L2-cache Examples: Intel Pentium II (Mendocino core), Pentium III (0.18μ technology), Pentium4, Athlon (Thunderbird core), Athlon 4, Duron (Spitfire core) D-cache I-cache L2-cache Processor Bus interface unit Processor bus L3 Cache System System Contr. Contr. Memory On-die L2-cache with an external front-end L3-cache Examples: Pentium 4 original design, K6-III D-cache I-cache L2-cache Bus interface unit Processor L3 Cache Processor bus System Contr. Memory On-die L2-cache with a direct coupled L3-cache Examples: Itanium