Lectures 6 and 7 Tour of Modern PC

A Tour of a Modern PC Motherboard and its

Devices

A typical modern computer will contain a motherboard that looks something like the figure below. The motherboard connects all the pieces of the computer together using various busses.

The computer has to provide power and typically cooling for the motherboard.

1

System Architecture

A modern computer system will implement a design similar to that shown below where the devices communicate over busses . We see that the CPU (the main processor) is connected by a front side bus (FSB) to a north bridge chip that connects to memory, graphics (via AGP) and a south bridge . The south bridge is connected to relatively slow devices such as PCI slots, disk drives, keyboards etc.

A motherboard for a modern PC

All the data transfers over the main system busses (front side bus, memory bus etc) are synchronised by a system clock . This clock typically runs at ...

Data is sometimes transferred on both the rising and falling edge of the clock signal, giving maximum data transfer rates of up to ...

2

Bus Operation – Parallel Data Transfers

The physical bus connections between the processor, north bridge, memory and graphics card etc each consist of an address bus, a data bus, and various control lines.

Example: Writing to Memory

When writing to memory, the

CPU puts a memory address on to the address bus in order to specify the memory slot (‘1’ in the diagram right). The CPU puts the data onto the data bus

(2) and then sets a control line

(called the Read/Write Enable line) to indicate to the memory that the data is to written to memory (3). The memory then writes the number into the correct memory slot.

Example: Reading from Memory

When reading a value in from memory, the first step is still to put the correct memory address on the address bus (1 in the diagram).

Then the CPU sets the Read/Write

Enable control to "Read" (step 2) and the memory puts the correct number on to the data bus (step 3).

The processor then reads this value.

(via North Bridge)

(via North Bridge)

3

Timing on a Bus

If we ask for some data, how do we know when it is ready? There are two solutions to this, being synchronous and asynchronous designs.

Synchronous data transfer:

Use a system clock

Components on the bus guarantee to have the data ready on time

Example: Reading memory

--------------------------------------------> time

The memory has to guarantee that the data will be ready within 2 clock cycles of a read command being given.

Asynchronous data transfer:

Use ‘handshaking’, ie wait for a signal that the data is ready.

A formal ‘protocol’ defines who waits when for what signal

Communication between a PC and a modem over a serial bus is an example of asynchronous communication

Timing is now not so crucial

4

Memory

Illiac Memory

Core memory (1951)

Memory consisting of tiny magnetic "donuts" at intersection of a lattice. Could be magnetized either "clockwise" or "counterclockwise". Fastest memory until late 1980's

A modern 256 Mb DDR-SDRAM DIMM (dual inline memory module)

Different Memory Approaches:

Dynamic random access memory (DRAM)

has memory cells with a paired transistor and capacitor. The memory requires constant refreshing to keep the capacitor charged. Cheap, and slow.

Static random access memory (SRAM)

uses multiple transistors, typically four to six, for each memory cell but doesn't have a capacitor in each cell. Fast, but expensive, it is used primarily for cache memory.

Flash RAM

uses 2 transistors; keeps its values with the power removed. Slow and expensive. Used in USB memory sticks, BIOS, etc

Current RAM technologies:

SD-RAM (Synchronous dynamic random access memory)

takes advantage of a ‘burst mode’ concept to improve performance by fetching the next bit in sequence before the previous one has finished. The idea is that most of the time the data needed by the CPU will be in sequence. Rate of data transfer set by system clock

DDR-SDRAM (Double Data Rate) SDRAM

transfers data on both rising and falling edge of system clock, so get a 266 MHz data rate with a 133

MHz system clock

5

Memory Errors, Parity Bits and Error Correction

The plastic packaging of memory contains small amounts of radioactivity that produce alpha particles. These are energetic, fast moving, helium atoms which are missing their electrons. When an alpha particle emitted by the packaging hits a sense line in the DRAM during a read cycle, the noise it produces causes the sense amplifier to misread the data. With 100 million computers in use today, we should expect roughly 6 million single bit errors per year.

Parity Bits: We can detect memory errors by adding an extra parity bit for every 8 bits of data. Let's look at even parity first. When the 8 bits in a byte receive data, the chip adds up the total number of "1"s. If the total number of "1"s is odd, the parity bit is set to "1." If the total is even, the parity bit is set to "0." When the data is read back out of the bits, the total is added up again and compared to the parity bit. If the total is odd and the parity bit is "1" then the data is assumed to be valid and sent to the CPU.

But if the total is odd and the parity bit is "0," the chip knows that there is an error somewhere in the 8 bits and dumps the data. Odd parity works the same way, but the parity bit is set to "1" when the total number of "1"s in the byte are even.

Parity Examples:

Data

Parity Bit

(even parity) Data

Parity Bit

(odd parity)

10110101

10010000

11111001

10110101

10010000

11111001

10101010 10101010

ECC-RAM uses additional bits to monitor the data in each byte. ECC uses several bits for error checking -- how many depends on the width of the bus -- instead of one.

ECC memory uses a special algorithm not only to detect single bit errors, but actually correct them as well. ECC memory will also detect instances when more than one bit of data in a byte fails. Such failures are very rare, and they are not correctable, even with ECC

6

IO and Other Devices

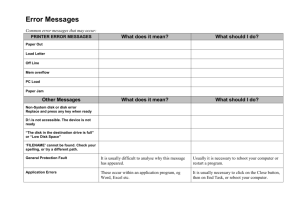

A typical list of devices is shown below.

7

Each device has a piece of software called a ‘driver’ or ‘device driver’ that is used by the operating system to control the device. The driver simply consists of one or more files containing code.

Each device can claim one or more numbered IO locations from the “Input/Output

Range” where data can be read from and written into the device by the CPU. (We already know that IO addresses 378

16

and 379

16

are part of the parallel port.) Devices can also use interrupts (by claiming a numbered “interrupt request”) and/or DMA

(Direct Memory Access) to communicate with the CPU; see next.

CPU Control of Input/Output Devices

There are three common methods for managing input and output operations.

•...

•...

•...

Programmed I/O (also known as Polling)

•Consider reading a block of data from a device.

•The CPU keeps checking the status of the device until it is ready to be read or written. This is known as a busy-wait .

•When the device is ready the transfer of data is made between the device and CPU.

8

•After the transfer is completed the CPU checks if there is another communication request for the device. If there is the process repeats, otherwise the CPU continues with another task.

Programmed I/O has several problems:

•...

•High priority devices are not checked until the CPU is finished with its current I/O task, which may have a low priority.

Interrupt driven I/O

•In interrupt driven I/O the device requests service through a special interrupt request line that goes directly to the CPU.

•The CPU then invokes an interrupt service routine (ISR) for the device and returns to normal execution when the ISR completes.

•With interrupt driven I/O the CPU does not access a device until it needs servicing, so it doesn’t waste time with busy-waits.

Direct memory access (DMA)

•Although interrupt driven I/O frees the CPU until the device requires service, the

CPU is still responsible for making the data transfer. All data travels over the bus twice: first to the CPU; then to the destination.

•A DMA device can transfer data directly to and from memory, rather than using the

CPU as an intermediary, and can thus relieve congestion on the bus.

Input/Output Devices

AGP= Accelerated Graphics Port

The video display card is typically connected by an AGP port to the CPU through the high-speed ‘north bridge’.

AGPx4 means 4 times faster than the original AGP standard. The video card can also use the slower PCI bus (see below).

9

PCI Bus (Peripheral Component

Interconnect)

Main way of connecting extra peripherals

Typical devices that use the PCI expansion slots include

EPROM

Flash memory that contains startup code for the BIOS (basic input output system).

Bios ‘boots up’ the computer before handing over to the operating system. It also manages the IO. The Bios can be upgraded by ‘flashing’ it with newer software.

Typical IO Ports

Communication (Serial) Port (COM1, COM2, …)

transmits a sequence of single bits, 1 bit at a time

asynchronous/synchronous transfer

use CTS (clear to send) and RTS (ready to send) lines for ‘handshaking’, ie controlling flow of data.

uses parity bits to check for errors.

10

Parallel Port (LPT1, LPT2, etc)

designed for talking to a printer, typically asynchronous/synchronous transfer

transmits 8 bits to a printer at a time.

-

Uses Busy, Strobe and Ack (acknowledge) to handshake.

-

Come in traditional, EPP and ECP flavours with varying capabilities.

Pin Description: (don’t learn!)

Base+0:

Base+1 = Status (input)

8 bit output

Bit7 Busy

Base+2 = Control Port (open collector)

Bit7 Reserved

Bit6 not ACK

Bit5 Paper Out

Bit4 Select In

Bit6 Reserved

Bit5 Enable Bidirectional

Bit4 Enable IRQ via ACK

Bit3 Select Printer

Bit3 not Error

Bit2 not IRQ

Bit1 Reserved

Bit0 Reserved

Bit2 Initialize Printer

Bit1 Auto Linefeed

Bit0 Strobe

Disk Drives

Disk drives connect via an IDE or EIDE bus. (ATA33/66/133

= different speed IDE protocols.) New drives use SATA

(serial ATA).

PIO=…

DMA=

11

Magnetic Disk Drives (eg Hard Disk, Hard Drive)

Long term, nonvolatile storage

Large, inexpensive, and slow

Lowest level in the memory hierarchy

Two major types:

Floppy disk and Hard disk

Both types of disks:

Rely on a rotating platter coated with a magnetic surface

Use a moveable read/write head to access the disk

Advantages of hard disks over floppy disks:

Platters are more rigid ( metal or glass) so they can be larger

Higher density because it can be controlled more precisely

Higher data rate because it spins faster

Can incorporate more than one platter

Most disks rotate at 3,600 to 7200 RPM

The smallest item of data that can be read or written is a sector . Many sectors make up a track. Traditionally all tracks have had the same number of sectors, but the sectors per track can change now to make use of the longer tracks near the outside of a disk.

Read/write data is a three-stage process:

Move the read/write head arm over the proper track

Wait for the desired sector to rotate under the read/write head

Read a sector as it passes under the read-write head

Disk File System :

Track

Sector

Cylinder eg ………………..…

Sectors are grouped into clusters, where a cluster is Head

Platter the smallest allocatable unit on the disk.

File system keeps list of used and unallocated (free)

Cylinder: all the tracks under the head at a given point on all clusters

A file uses 1 or more clusters. surfaces.

File system controls access (open, read, write, close) to files

12

Example: on drive “T:”, any file will take up some multiple of .......

13

Raid

“Redundant array of inexpensive disks”. Connect multiple hard drives together to form what appears to be one drive. Can implement Raid at a range of different levels: (see: http://arstechnica.com/paedia/r/ra id-1.html)

Striping (Raid 0)

-

-

Mirroring (Raid 1)

-

-

Redundancy (Raid 3)

Aim to protect against a single drive failing without cost of mirroring

Typically allows ‘…………………………’ - unplug failed drive, plug in new one, while system still up and running.

Redundancy implementation:

Uses XOR to store extra copy of data.

Revision:

0 XOR 0 =

0 XOR 1 =

1 XOR 0 =

1 XOR 1 =

Example:

1010 1111 XOR 1100 0011 =

1010 1111 XOR 0110 1100 =

0110 1100 XOR 1100 0011 = c = a XOR b a = XOR b = XOR

Disk 1 Disk 2 Disk 3 Disk 4

Data A

Hex 65 r

114 s

115 t

116

Binary 01000001 01110010 01110011 01110100

Disk 5

Redundancy Data

Disk 1

Data A

Hex 65 dead

?

Disk 3 Disk 4 s

115 t

116

Disk 5

Redundancy Data

Binary 01000001 01110011 01110100

Computer Mice

In 1968, at the Fall Joint Computer Conference, Engelbart revealed for the first time such futuristic technology as the mouse, w ord processing, and on-line networking, technology. This eventually led to the development of the Xerox PARC Star personal computer at Xerox's PARC , which in turn was the inspiration for the Apple

Macintosh .

14

How roller-based Computer Mice Work by Marshall Brain, From HowStuffWorks.com http://www.howstuffworks.com/mouse.htm?printable=1

Mice first broke onto the public stage with the introduction of the Apple Macintosh in 1984, and since then they have helped to completely redefine the way we use computers! Every day of your computing life, you reach out for your mouse whenever you want to move your cursor or activate something. Your mouse senses your motion and your clicks and sends them to the computer so it can respond appropriately.

Inside a Mouse

The main goal of any mouse is to translate the motion of your hand into signals that the computer can use.

Almost all mice today do the translation using five components:

Mice come in all shapes and sizes.

This is an older two-button mouse chosen for its simplicity.

The guts of a mouse

1.

A ball inside the mouse touches the desktop and rolls when the mouse moves.

The underside of the mouse's logic board. The exposed portion of the ball touches the desktop

2.

Two rollers inside the mouse touch the ball. One of the rollers is oriented so that it detects motion in the X direction, and the other is oriented 90 degrees to the first roller so it detects motion in the Y direction. When the ball rolls, one or both of these rollers roll as well. The following image shows the two white rollers on this mouse:

The rollers that touch the ball and detect X and Y motion

15

3.

The rollers each connect to a shaft, and the shaft spins a disk with holes in it. When a roller rolls, its shaft and disk spin. The following image shows the disk:

A typical optical encoding disk. This disk has 36 holes around its outer edge.

4.

On either side of the disk there is an infrared LED and an infrared sensor.

The holes in the disk break the beam of light coming from the LED, so that the infrared sensor sees pulses of light. The rate of the pulsing is directly related to the speed of the mouse and the distance it travels.

A close-up of one of the optical encoders that track mouse motion. There is an infrared LED (clear) on one side of the disk and an infrared sensor (red) on the other.

5.

An on-board processor chip reads the pulses from the infrared sensors and turns them into binary data that the computer can understand. The chip sends the binary data to the computer through the mouse's cord and PS/2 connector.

The logic section of a mouse is dominated by an encoder chip, a small processor that reads the pulses coming from the infrared sensors and turns them into bytes sent to the computer. You can also see the two buttons that detect clicks (on either side of the wire connector).

A typical PS/2 Connector. Assume that pin 1 is located just to the left of the black alignment pin and the others are numbered clockwise from there.

By using two LEDs for each wheel, we can determine the direction the mouse is moving. The simplified figure below shows a wheel in 4 different states, each 15° rotated from the last. Diagram E is equivalent to diagram A, being 60° rotated. For

16

clockwise rotation the states follow each other in order A-B-C-D-E from left to right but if you read the states from right to left, E-D-C-B-A, then these correspond to anticlockwise rotation. These give the timing diagram shown below; read this left to right for the A-B-C-D-E order, and right-to-left for the E-D-C-B-A order. a b

How can we tell which way the mouse is moving?

17

CPU Evolution

ENIAC (1946)

Addressable Memory: 200 digits

18,000 vacuum tubes,6,000 switches,10,000 capacitors,70,000 resistors,1,500 relays

30 tons

10 feet tall x 1,800 square feet

5,000 additions / second

1,000 times faster than any calculating machine before it.

Intel 4004 (Nov 15 1971)

•First ever microprocessor

•Clock speed: 108 kHz

•Bus width: 4 bit

•Transistors: 2,300

•Track width: 10 µm

•Addressable memory: 640 byte

•0.06 MIPS

Intel 8088 (1979)

(used in first IBM PC, 1981)

Clock speed 4 MHz

0.33 MIPs

Bus width 16 bits (internal) 8 bits (external)

Addressable memory: 1 Mb

Transistors: 29,000

Track width: 3 µm

The first PC had 16 kByte RAM, expandable to 256k.

Intel Pentium III (1999)

•Clock speed: 1 GHz (in 2001)

•Bus width: 64 bit

•Transistors: 9,500,000

•Track width: 0.25 µm

•Addressable memory: 64 GByte

Intel P4 (2001)

•Clock speed:

•Bus width: 64 bit

•Transist ors:

•Track width: 0.18 µm

•Addressable memory: 64 Gbyte

Volts: 1.75

Power:

First PC – IBM, 1981

18

Pentium 4 Prescott 3.4 GHz (2004)

•Clock speed: 3.4 GHz

•Bus Width: 64 bit

•Transistors: 125 million

•Track Width: 0.09 µm

•Addressable Memory:

•Voltage: 1.385V

•Power: 100 Watts

•Addressable Memory: 64 Gbyte

AMD Processors:

Athlon XP 2.2 GHz (2003)

•Clock speed:

•Bus width: 64 bit

•Transist ors:

•Track width: 0.13 µm

•Addressable memory: 64 Gbyte

•Volts: 1.75

•Power:

Athlon XP 64 (2004)

•Clock speed:

•Bus width: 64 bit

•Transist ors:

•Track width: 0.13 µm

•Addressable memory:

•Volts: 1.75

•Power:

•Registers:

•Direct access to memory (figure below)

19

Moore’s Law

In 1976, Gordon

Moore (CEO, Intel) predicted that the number of transistors per integrated circuit would double every

18 months. This prediction appears to still be correct.

PC CPUs

1st. Generation

2nd. Generation

3rd. Generation

8086 and 8088

80286

Year

1978-81

1984

80386DX and 80386SX 1987-88

4th. Generation

5th. Generation

Improved

5th. Generation

80486SX, 80486DX,

80486DX2 and 80486DX4

1990-92

Pentium

Cyrix 6X86

AMD K5

IDT WinChip C6

1993-95

1996

1996

1997

Pentium MMX

IBM/Cyrix 6x86MX

IDT WinChip2 3D

6th. Generation

Improved 6th. Generation

7th. Generation

Pentium Pro

AMD K6

Pentium II

AMD K6-2

Mobile Pentium II

Mobile Celeron

Pentium III

AMD original Athlon

AMD Athlon Thunderbird

Pentium 4

Today

Major challenge in CPU design:

Possible solutions:

Over-clocking

Pentium 4 Prescott

Athlon 64

1997

1997

1998

1995

1997

1997

1998

1999

1999

2000

2001

2004

2004

Transistor count

29,000

134,000

275,000

1,200,000

3,100,000

--

--

3,500,000

4,500,000

6,000,000

6,000,000

5,500,000

8,800,000

7,500,000

9,300,000

27,400,000

18,900,000

9,300,000

22,000,000

37,000,000

42,000,000

125,000,000

105,000,000

20