DEPARTMENT OF COMPUTER APPLICATIONS

advertisement

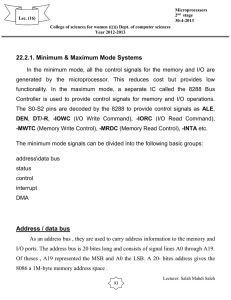

DEPARTMENT OF COMPUTER APPLICATIONS MC932 – MICROPROCESSORS AND ITS APPLICATIONS 2 marks question answers Unit - I: 1. Additional features of 8086: It supports a 16 bit ALU, a set of 16 bit registers and provides segmented memory addressing capacity, a rich instruction set, powerful interrupt structure, fetched instruction queue for overlapped fetching and execution etc. 2. Two parts of 8086: BIU – Bus Interface unit, EU – Execution Unit. 3. BIU components : It contains the circuit for physical address calculation and predecoding instruction byte queue. 4. EU components : It contains the register set of 8086 except segment register and IP. It has a 16 bit ALU, able to perform arithmetic and logic operations. 5. Memory segmentation : The complete physical address is divided into a number of logical segments. Each segment is 64 k bytes in size and is addressed by one of the segment registers. 6. Flag register : It contains Condition code or Status flag and Machine control Flags. 7. Condition Code flag register : It is the lower byte of the 16 bit flag register along with the overflow flag.\ 8. Machine Control flag register : It is the higher byte of the flag register of 8086. 9. Parts of control flag register: (i) Direction flag (D) (ii) Interrupt flag (I) (iii) Trap flag (T). 10. Addressing Mode : It indicates a way of locating data or operands. 11. Types of Instruction : Sequential control flow instruction, control transfer instruction are the two types of instructions. 12. MOV : This data transfer instruction transfers data from one register/ memory location to another register/memory location. 13. PUSH : This instruction pushes the contents of the special register / memory location on to the stack. 14. Data copy / Transfer Instruction : It is used to transfer data from source operand to destination operand. 15. POP : This instruction loads the specified register/ memory location with the contents of the memory location of which address is formed using the current stack segment. 16. XCGG : This instruction exchanges the contents of the specified source and destination operands. 17. Arithmetic Instruction : It performs the arithmetic operations like addition, subtraction, multiplication and division along with the respective ASCII and decimal adjust instructions. 18. Logical Instruction: They are used for carrying out the bit shift, rotate, basic logical operations. 19. String manipulation Instruction : A series of data bytes or words available in memory at consecutive locations, to be reference to collectively or individually called as byte string or word string. 20. Control Transfer or Branching Instruction: The control transfer instruction transfer the flow of execution of the program to a new address specified in the instruction directly or indirectly. 21. Types of Branch Instruction : Unconditional Control Transfer Instruction and Unconditional Control Transfer Instruction are the two types of branch instruction. 22. Types of control Instruction : Flag manipulation and Process control instruction are the types of Control Instruction. 23. Calling Program: The main program which call the subroutine by passing data or constant is called calling program. 24. Procedure parameters type: Public and extern are the types of procedure parameters. 25. Interrupt service Routine : The CPU is executing a program an ‘interrupt’ breaks the normal sequence of execution of instructions, diverts its execution to some other program is called ISR. Unit – II: 1. Timing diagram : Every instruction requires a definite number of clock cycles for its execution. Thus every instruction requires a fixed amount of time. 2. Two parts of timing diagram : Timing diagram for read cycle or Timing diagram for write cycle are the two parts of timing diagram. 3. Different Signals : ALE – Address Latch Enable Signal M/IO – Memory or I/O operation. RD – Read Control Signal. WR – Write Signal. DT/R – Direction of Data. 4. HOLD & HLDA Signals: HOLD pin is checked at the end of each bus cycle. When the request is dropped by the requesting master, the HLDA is dropped by the processor at the trailing edge of the next clock 5. Components of 8086 : Set of registers known as general purpose and special purpose registers. All of them are 16 bit registers. 6. Different general data registers used in 8086 AX,BX, CX, DX AX – 16 bit accumulator BX – Offset storage of physical address CX – default count 16 bit register. DX – Used as an implicit operand or destination. 7. Components of AX : AL – Lower 8 bit. AH – Higher 8 bit. 8. Segment Register : Microprocessor memory can be dividing into 16 logical parts. Each part is of 64 kilo bytes of memory. 9. Four segment registers : Code Segment Register (CS), Data Segment Register (DS), Extra Segment Register (ES), Stack Segment Register (SS) 10. How the physical address is calculated? The physical address is calculated from two parts, the first is segment address and the second is offset. 11. Pointers : Contains offset within the particular segment. IP, BP and SP are usually containing offset within the code JP and stack (BP & SP) segments. 12. Index Register : It is used as general purpose registers as well as for offset storage. 13. Flag Register : It indicates the results of computations in the ALU. 14. Group of 8086 signals: Signals having common functions in minimum of max mode. Signals which have special functions for minimum mode. Signals having functions for maximum mode. 15. RD : Read Signal when low indicates the peripherals that the processor is performing a memory or I/O read operation. 16. READY : It is acknowledgement from the slow devices or memory that they have completed the data transfer. 17. TEST : This input is examined by a ‘WAIT’ instruction. 18. RESET : This input causes the processor to terminate the current activity and start execution from FFFF off. 19. DT / R : Data Transmit /Receive. This output is used to decide the direction of data flow through the transreceiver to separate the data from multiplexed address /data signal. 20. DEN : Data enable. This signal indicates the availability of valid data over the address / data line. 21. INTA : Interrupt Acknowledgement. This signal is used as a read store for interrupt acknowledgement cycles. 22. ALE – Address Latch Enable: This output signal indicates the availability of the valid address on the address / data. Unit - III: 1. Types of semiconductor : Static RAM, Dynamic RAM. 2. Two types of cycles: Refresh Cycle, Memory read cycle. 3. Methods of Interfacing I/O devices : I/O mapped, Memory mapped. 4. Mode 0 : This mode of operation is generally called an interrupt on terminal count. 5. Mode 1 : This is called as programmable one-shot mode or monostable multivibrator. 6. Mode 2: This is called rate generator or divide by N counter. 7. Mode 3 : This is called as square wave rate generator. 8. Mode 4 : This is called software triggered stobe. 9. Types of write operation in 8253: Writing a control word into a control word register. Writing a count value into a count register. 10. Uses of control word register content : a) Initializing the operation mode. b) Selection of counters. c) Choosing binary IBCD counters. d) Loading of the counter register. 11. Two methods for reading 8253 counter register: Clock or the counting procedure. Reading a counter or Reading on fly. 12. Operating modes of 8259: Fully nested mode, End of interrupt, Automatic rotation, Automatic EOI mode, Specific Rotation, special mask mode. 13. I/O control and Data Buffer : Controls the flow data to / from the 8279. 14. Control and timing register and timing control : These registers store the keyboard and display modes and other operating conditions programmed by CPU. 15. Scan counter : It has two modes to scan the key matrix and refresh the display. 16. Modes of operation of 8279: Input (keyboard) modes and Output (Display) modes. 17. DMA : Direct Memory Access of data transfer is the fastest among all the modes of data transfer. 18. 8257 parts : DMA address register, terminal count register. 19. Common register for all channel : Mode set register and status registers. 20. Function of DMA Address Register: It is to store the address of the starting memory location, which will be accessed by the DMA channel. 21. Terminal Count Register : It is used for ascertaining that the data transfer through a DMA channel or stops at the required number of DMA cycles. 22. Mode Set Register: It is used for programming the 8257 as per requirements of the system. 23. MARK : The modulo 128 mark output indicates to the selected peripheral that the current DMA cycle is the 128th cycle. 23. Different Signals: ALE – Address Latch Enable Signal. M/IO – Memory or I/O operation. RD – Read Control Signal. WR – Write Signal. DT/R – Direction of data. 24. HOLD & HLDA Signals : HOLD