XMOD-trainer 2014.08.05

advertisement

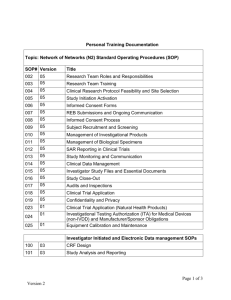

XMOD-trainer 2014.08.05 Krista M. Hill (kmhill@hartford.edu) August 5, 2014 This is documentation for the XMOD logic trainer. Copyright Krista Hill (kmhill@hartford.edu) and is licensed under the CERN Open Source Hardware License (OHL) version 1.2. You may redistribute and modify this documentation under the terms of the CERN OHL v.1.2. (http://ohwr.org/cernohl). This documentation is distributed WITHOUT ANY EXPRESS OR IMPLIED WARRANTY, INCLUDING OF MERCHANTABILITY, SATISFACTORY QUALITY AND FITNESS FOR A PARTICULAR PURPOSE. Please see the CERN OHL v.1.2 for applicable conditions 1 Introduction While 3.3 Volt logic is an industry standard for digital logic, currently we are not aware of any available trainers for teaching digital logic design, commercial or otherwise, so we designed our own. Our trainer can be constructed as a nished design with a printed circuit board mounted on a bread-board, or can be breadboarded using discrete parts. Our trainer can be used with discrete logic such as 74HC or with CPLD modules such the Digilent Inc.,[5] CMOD using a Xilinx[8] Coolrunner-II CPLD or our XMOD[7] module using a Xilinx XC9536xl CPLD. In planning the nished design our rst signicant decision was to ease the construction and maintenance by using only through-hole parts. We also wanted the trainer to be inexpensive, so we simplied the construction by involving a generic solderless breadboard. We also decided that the trainer would provide basic resources such as 3.3 Volt power, logic inputs, logic indicators, a debounced push-button switch, a clock generator, and a logic probe. Section 2 outlines our logic trainer. Section 3 outlines how you can assemble a nished trainer. Section 4 presents the actual circuitry so you can breadboard the logic trainer yourself. The XMOD-trainer is part of the XMOD project [7] and is released under the terms of the CERN Open Source Hardware License[2]. 2 Assembled Logic Trainer Figure 1 shows how the trainer is constructed on a PC board which is mounted on a solderless breadboard and is used with a wall mounted power adapter. The 3.3 Volt logic trainer includes the basic resources needed for the construction of logic circuits in an undergraduate laboratory setting. The trainer can be used with dual in-line package (DIP) type logic devices and is compatible with 3.3 Volt power and 3.3 Volt signals. Both the CMOD[5] and XMOD[7] modules each contain a CPLD and can be used with the trainer. This section outlines the assembled trainer. Section 3 outlines how you can have a nished trainer assembled. Section 4 presents the actual circuitry so you can breadboard the logic trainer yourself. The XMOD-trainer is licensed under the CERN-OHL v.1.2[2] 1 Figure 1: Logic circuits trainer Figure 2 outlines the trainer PC board. The gure is annotated according to the following list of features provided. The pins in each connector block (P1, P2, P3) are arranged in columns numbered 1 through 9. • The power connector is JP, the power switch is SWP, the power indicator LED is LP, and FB1 is a ferrite bead. • The clock signal generator switch (CFS) selects 1 Hz, 10 Hz, or 100 Hz. • The Sources connector block (P3) has ground (GND), 3.3 Volt power (VCC), and the clock (CLK). The VDD pins allow for a second power supply Voltage that is not currently used. • Eight logic switches (SW1 to SW8) produce logic signals. • The push button (PB) provides a bounce-free logic signal. • The switches connector block (P1) has the logic switch (SW1-SW8) output signals and the push button (PB) output signal.. • The Indicators connector block (P2) has pins for the logic indicators (L1-L8) and logic probe (PX). • Eight LED logic indicators (L1 to L8) each indicate a logic-high input. • The logic probe LEDs indicate logic-low (PXL) and logic-high (PXH) • The indicators connector block (P3) has inputs for the LED indicators (L1 to L8) as well as the logic probe (PX) The circled plus symbols represent mounting screws, the dark boxes each represent a chip mounted in a socket. A track about the periphery of the board is connected to ground. 2 Figure 2: Logic trainer PC board outline 3 Trainer Assembly In planning the logic trainer design the rst signicant decision was to ease the construction and maintenance by using only through-hole parts. We also wanted the trainer to be inexpensive so we simplied the construction by using a generic solderless breadboard. We also decided that the trainer would include only basic resources. In our electronics lab each station has a multimeter, oscilloscope, and a personal computer. All the logic trainer artwork is released according to the CERN Open Source Hardware License, outlined in section 6. The full artwork is on the XMOD project[7] page.There are numerous companies that can produce the logic trainer PC board from our artwork and we have had good experience with Alberta Printed Circuits [1]. Likewise there are numerous parts suppliers and we have had good experience with Digi- Key [4]and Jameco Electronics [6]. There are numerous companies that assemble nished PC boards at a premium, however we typically assemble our own PC boards in-house. 4 Trainer Circuit This section presents the logic trainer circuitry to aid your understanding so that you can make some decisions how or how much of the the circuitry you might want to build by hand. Figure 3 shows the an example with the complete logic trainer powered and is powered with a pair of D-cells. The chips to the right are an example circuit being tested. The DIP-switch package near the top provides switch input and the LEDs to the bottom display the output. Each major part of the logic trainer in discussed in the following. The logic input part provide switch and push-button input. There is a clock signal generator. The logic indicators indicate when a signal is logic-high. The logic probe diers from the indicators as it can also indicate when a logic signal is logic-low. In considering a fast clock both probe LEDs appear to glow. Be warned that the part designators shown below may dier from those used in the schematic for the nished design. 3 Figure 3: Logic trainer breadboard with example circuit Figure 4 shows the logic input switches. The switches SW1A through SW1H are the individual elements of an 8-switch DIP-switch package. With six inverters in a package this part of the circuitry uses only two chips, with four gates left over. The DIP package is arranged so that when each switch is in an up-ward position the corresponding element is closed, causing the corresponding gate output to be logic-high. The pulse generator in Figure 5 is essentially a debounce circuit. The phenomenon of switch-bounce occurs in the order of milliseconds. The push-button switch SW2 resistance is less than 0.10 Ohm so that the discharge time constant T1 is much less than switch-bounce so that any switch closure will discharge C1, causing the gate to produce a high pulse output. With SW2 open, the output remains high until C1 charges to half the power supply Voltage, which is approximately 32.6msec with the selected values. Figure 6 is the schematic for the clock signal generator. The values for R10 and C2 are chosen for the clock frequency to be approximately 1 Hz. With a resistor R11 optionally placed in parallel with R10, the frequency is increased. Three cases are given in Table 1. The frequency in Hertz for the clock is given by equation 1 where Re is R10 in parallel with R11 and Ce is the sum of C2 and C3. Fc ≈ 0.7213 Re Ce 4 (1) Figure 4: Logic input switches Figure 5: Logic pulser Figure 6: Clock signal generator 5 Table 1: Clock Generator resistor choices R11 Re Frequency None 750K 1 Hz 82K 73.9K 10 Hz 7.5K 7.43K 103Hz The functional principle of the circuit is that capacitors C2 and C3 act as a Voltage divider, ensuring that Voltage Vc1 stays within the range of the power supply. Capacitors C2 and C3 as well as U2C and U2D generate the clock signal and U2E serves as a buer. Figure 7 shows Voltage waveforms for Vc1 and Vc2. In comparison to the time for a gate to transition the resistors cause the capacitors to charge and discharge more slowly, When Vc1 returns back to the device threshold Voltage, the positive feedback through U2C, U2D, and the capacitors causes the clock state to change suddenly. In Figure 7 the components chosen for 103 Hz were used. The actual measured frequency was 104 Hz and the duty cycle is 46%. These approximate values should be reasonable for use with the trainer. Figure 7: Clock signal generator waveforms The logic indicators indicate when a given input is logic-high. Figure 8 shows that an inverter provides a threshold test for each LED. When a given input is above the logic threshold the inverter output becomes low, so that a Voltage appears across the corresponding LED so that it lights up. With the logic indicators four gates at most are used per chip so that the total current will be within the recommended current range. The logic probe shown in Figure 9 diers from a logic indicator in that the probe can also indicate when a signal is logic-low. The probe uses two LEDs to indicate the following three Voltage ranges. For a fast clock signal however, both LEDs will appear to light up. • Voltages higher than 2.42V cause D9 (H) to light up • Voltages between 0.88V and 2.42V cause neither D9 or D10 to light up • Voltages lower than 0.88V cause D10 (L) to light up In constructing the trainer circuitry there are some details to be aware of. First o, given the very high input impedance, unused gate inputs should connected in a way to force the input to a known state. In breadboarding this test circuit unused gate inputs were tied to ground but in the layout the power supply was used. A minor issue involves seating the DIP-switch package in the breadboard. Make sure the pins are long enough and on the underside of the DIP-switch package there might be some protruding bumps. If the bumps cause a problem with seating the DIP-switch package on the breadboard, we suggest that you use a tool such as a utility knife to remove the bumps. Consider using hot-melt glue as well to mount the DIP-switch package. 6 Figure 8: Logic indicators Besides the parts shown here additional parts include a 100uF power supply lter capacitor, a 0.1uF ceramic capacitor for each chip as well as D11 and R35 which can be used as a power indicator. Besides these parts, a regulated 3.3 Volt power cube or a pair of battery cells can provide power for a time. 5 Closing Words The XMOD-trainer was designed because we needed it at a time when there was no other choice that we were aware of. We chose the CERN-OHL[2] as it encourages rapid dissemination of design ideas. If you make use of any of the material that was developed, then please, we would like to hear about how things are going or have gone. 6 Open-Source Hardware License The XMOD project hardware documentation included in this book is made available under the terms of the CERN Open Hardware License (COHL)[2]. The license denes the conditions under which a licensee will be able to use or modify the licensed material. The COHL was originally written for CERN designs hosted in the Open Hardware Repository[3]. The license can be used by anyone to share design information under the specic license terms. The concept of COHL shares the same principles as open source software. Anyone should be able to see the source or hardware design documentation and be able to study, modify, and share it, as well as sell the resulting hardware. The license includes a restriction that if modications are made and distributed, 7 Figure 9: Logic probe it must be under the same license conditions. This is the persistent nature of the license, which means that as a gift to the community, the whole community will continue to benet from improvements that are shared back with the community. The full legal denition of the COHL [2] is posted on the Open Hardware Repository website. 7 Bibliography References [1] Alberta Printed Circuits, http://www.apcircuits.com/ [2] CERN Open Hardware License, http://www.ohwr.org/projects/cernohl/ [3] CERN Open Hardware Repository, http://www.ohwr.org/ [4] Digi-Key Corp., http://www.digikey.com/ [5] Digilent Inc., http://www.digilentinc.com/ [6] Jameco Electronics, http://www.jameco.com/ [7] XMOD Project, http://uhaweb.hartford.edu/kmhill/projects/xmod/ [8] Xilinx, http://www.xilinx.com/ 8