MSC8144ADS Processor Board Reference Manual

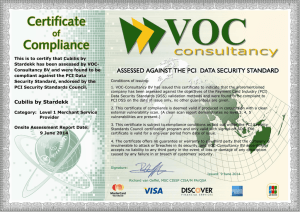

advertisement