Mixed-Signal Design in FDSOI

advertisement

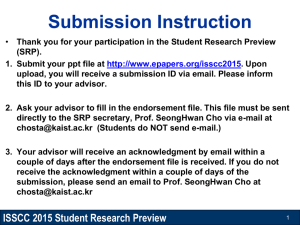

Mixed-Signal Design in FDSOI Boris Murmann June 22, 2015 Outline Application trends and needs Review of FDSOI advantages Examples › High-speed data conversion › RF transceivers › Medical imaging › Machine learning 2 The Big Picture Hardware Platforms Physical World Software, Networks Virtual World Fusion of Physical and Virtual Worlds Various terminology for the same overarching trend › Third paradigm › Ubiquitous computing › Internet of Everything 3 The Internet of Everything Source: Vivante Corporation 4 This Trend is Real and Here to Stay Reference: Kim, Keynote Talk, ISSCC 2015 5 Expected Impact of Wearable Devices on Data Traffic Source: Cisco VNI Mobile, 2015 6 Implications Unprecedented opportunities for new businesses › Uber, anyone? New forms of human-machine interaction › Augmented reality, wearable devices, … New kinds of sensors, actuators › Medical diagnostics, robotics, … Fundamental change in the nature and volume of data › Vast amounts of data at the “edge” requiring local processing › Cloud computing ↔ fog computing 7 Selected Needs in Mixed-Signal/RF Design Ultra low-power analog interfaces Ultra low-power fog computing 8 Universal radios Ultra high-speed, low energy data links Outline Application trends and needs Review of FDSOI advantages Examples › High-speed data conversion › RF transceivers › Medical imaging › Machine learning 9 Variability Tighter process corners and less random mismatch than competing processes [Le Tual, ISSCC 2014] Benefits › Simpler design process, shorter design cycle › Improved yield or improved performance at given yield Bulk FDSOI Performance Gain in Guaranteed Performance 10 Switch Performance Improved gate control allows for small VTH Backgate bias allows for additional VTH reduction on demand Result is an unprecedented quality of analog switches Key for high-performance data converters and other SC circuits Compounding benefits: Smaller R Smaller switch Compact layout Lower parasitics Even smaller switch 11 [Le Tual, ISSCC 2014] Junction Capacitance Low Cj makes a substantial difference in high-speed design › Drastic reduction of self-loading in gain stages › Drastic reduction of switch self-loading This not only leads to incremental improvements, but allows the designer the use circuit architectures that would be infeasible/inefficient in bulk technology › Some examples to follow 12 Outline Application trends and needs Review of FDSOI advantages Examples › High-speed data conversion › Medical imaging › RF transceivers › Machine learning 13 Increasing Need for Bandwidth 14 Motivation – Increasingly Complex Modulation Both electrical and optical systems are trending away from simple NRZ signaling Requires linear front-end circuits and very highspeed A/D converters Reference: K. Roberts et al., IEEE Communications Magazine, July 2010 15 ADC Landscape in 2005 4 FoM W [fJ/conv-step] 10 40 GS/s, 10W 2 10 𝑃 𝐹𝑂𝑀𝑊 = 𝑓𝑠 ∙ 2𝐸𝑁𝑂𝐵 𝑓 𝑓𝑖𝑛 ≅ 2𝑠 0 10 4 10 5 10 6 10 7 8 10 10 f s [Hz] Data: http://web.stanford.edu/~murmann/adcsurvey.html 16 9 10 10 10 11 10 ADC Landscape in 2010 4 FoM W [fJ/conv-step] 10 2 10 0 10 4 10 5 10 6 10 7 8 10 10 f s [Hz] Data: http://web.stanford.edu/~murmann/adcsurvey.html 17 9 10 10 10 11 10 ADC Landscape in 2015 4 FoM W [fJ/conv-step] 10 2 10 0 10 4 10 5 10 6 10 7 8 10 10 f s [Hz] Data: http://web.stanford.edu/~murmann/adcsurvey.html 18 9 10 10 10 11 10 28 FDSOI or 32 SOI ADC Landscape in 2015 4 FoM W [fJ/conv-step] 10 2 10 0 10 4 10 5 10 6 10 7 8 10 10 f s [Hz] Data: http://web.stanford.edu/~murmann/adcsurvey.html 19 9 10 10 10 11 10 State of the Art: 8b, 90 GS/s, 667 mW Reference: Kull et al., ISSCC 2014 20 Architecture Two switches in series Takes advantage of SOI Reference: Kull et al., ISSCC 2014 21 RF Goes Switch-Cap Universal Radios? Paradigm shift toward translational circuits, N-path filters Enabled by switch performance in modern CMOS technology FDSOI provides same advantages as seen in the data converter examples Reference: J. Park and B. Razavi, “Channel Selection at RF Using Miller Bandpass Filters,” IEEE J. Solid-State Circuits, vol. 50, pp. 3063-3078, Dec. 2014. 22 Ultrasound Goes Handheld and Wearable A. Bhuyan eXo System Butterfly Network Source (bottom): http://www.ultrasoundschoolsinfo.com/next-wave-ultrasound-technology/ 23 Work in Progress: Integrated Ultrasound Receiver Ultrasound transducer 24 Work in Progress: Integrated Ultrasound Receiver Conventional Front-End Architecture Expensive cable Proposed Front-End Architecture Pixel pitch-matched analog front-end (250 x 250 mm2) Each pixel contains an 11b, 10MHz ADC occupying only 100 x 100 mm › Enabled by inverter-based amplification › Possible due to small junction caps, large gm/gds of 28nm FDSOI 25 Area of State-of-the-Art DS Modulators BW=5MHz~25MHz, and SNDR=50dB~75dB 2 10 SDCT(ISSCC) SDCT(VLSI) 16SDSC(ISSCC) Channel SDSC(VLSI) 1 Area [mm2] 10 0 10 Digital -1 10 pixel area [2] [1] [3] -2 10 -3 10 This DS 10 28nm FDSOI [2009, Van Veldhoven, 40nm process]0 -1 -2 10 Power [W] [1] Van Veldhoven, VLSI 2009 - 40nm [2] K. Matsukawa, VLSI 2012 - 40nm 26 [3] E. Z. Tabasy, VLSI 2013 - 22nm 10 Trend Toward Machine “Intelligence” [IEEE] Driverless cars, gesture control, security, language translation, … 27 Example: Image Classification Many interesting problems to solve Wide range of algorithms and complexity Sources: Choi, ISSCC 2015; http://image-net.org/challenges/LSVRC/2013/index; D. Hammerstrom 28 Are We Ready? Source: http://funnypicsx.com/wp-content/uploads/funny18/The-first-portable-computer.jpg 29 Today’s Digital Systems Won’t Cut It! Source: Hammerstrom, DARPA 30 Example: Lane Following for a Self-Driving Car … … … “Sea” of dot products Image Source: Adam Coates, 2014 31 ~50 million coefficients memory bottleneck ~100 W on a GPU board Work Toward Custom Chips Area: 67.7 mm2 Main idea: Bring memory closer to computation Read from 256-bit, 36MB eDRAM: ~19 pJ (off-chip DRAM is ~6 nJ) Advancements in 3D integration will improve this further And some point we should become compute-limited › Opportunity for analog computing? Reference: Y. Chen, MICRO 2014 32 Digital Multiplier 33 Passive Charge-Redistribution Multiplier Purely passive multiplication via a specially designed switching sequence Unit capacitances can be as low as 100 aF FDSOI greatly helps reduce parasitics, improve switch performance QP SIGN + 8Cu 4Cu 2Cu Cu VDD/2 vOD 8Cu 4Cu QN 34 Cu − SIGN Reference: Bankman & Murmann, Electronics Letters, 2015 2Cu Example: 12 x 9 𝑄𝑊 = 12𝐶𝑢 𝑉𝑟𝑒𝑓 12 𝑉𝑊 = 𝑉 15 𝑟𝑒𝑓 𝑄𝑊𝑋 = 𝑉𝑊𝑋 35 12 𝑉𝑟𝑒𝑓 ⋅ 9𝐶𝑢 15 12 9 = ⋅ 𝑉𝑟𝑒𝑓 15 15 VREF 8Cu 4Cu 2Cu Cu RESET 8Cu 4Cu 2Cu Cu INW 8Cu 4Cu 2Cu Cu SHARE 8Cu 4Cu 2Cu Cu INX 8Cu 4Cu 2Cu Cu SHARE (Logical inverse of 9) Complete Charge Domain Dot Product Kernel Key idea: Internally “analog,” externally digital dot product kernel Basic operation used to realize a trained artificial neuron Many D/A multiplier cells are connected together for charge sharing Dot product signal is converted back to digital to feed the next layer of the neural network 36 Case Study: MNIST Handwritten Digits Input layer, hidden layer, softmax layer Generalizes logistic regression to multiple classes/categories 37 Comparison with Digital Dot Product (28nm FDSOI) 38 Summary The transition to the “third paradigm” brings interesting opportunities and challenges › Mixed-signal IC design is no exception FDSOI technology offers significant benefits toward addressing the resulting needs › Ultra low-power fog computing › Densely integrated, low-power analog interfaces › Universal radios › Ultra high-speed ADCs › … 39 Questions? 40