Timing Analysis

Introduction

The goal of timing analysis is to verify that a design meets timing requirements under a specified set of

timing constraints, such as arrival and required times, operating conditions, slew rates, false paths, and

path delays. Performing timing analysis lets you determine how fast a design can run without incurring

timing violations. You can use the results of timing analysis to fine tune and debug the speed-limiting,

critical paths in a design

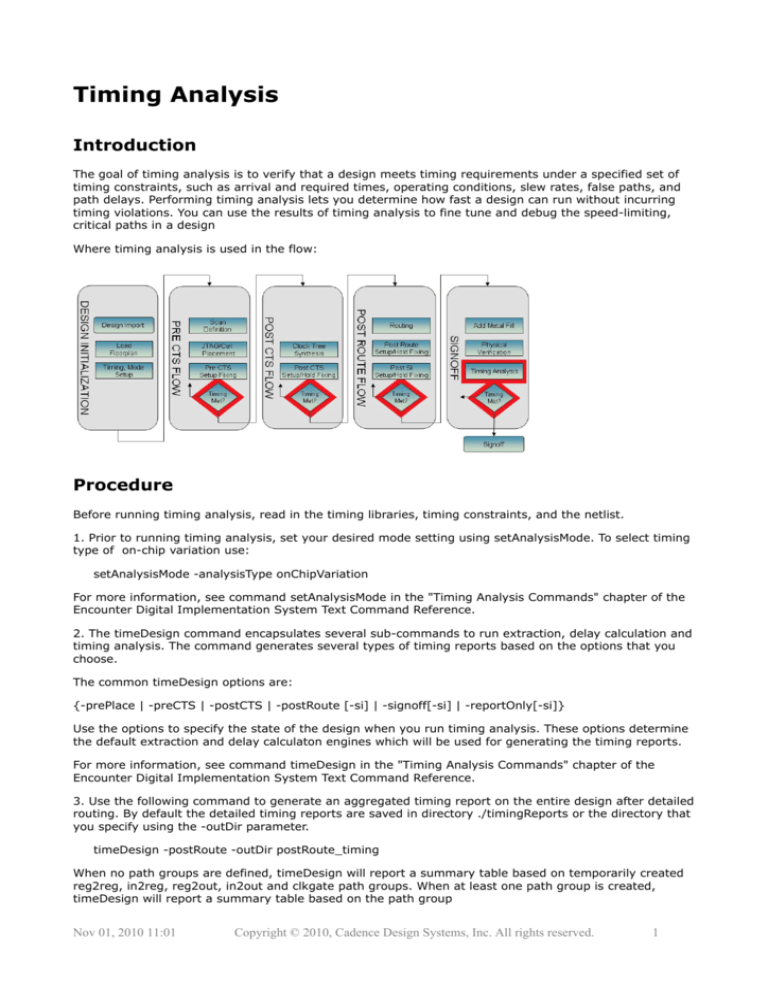

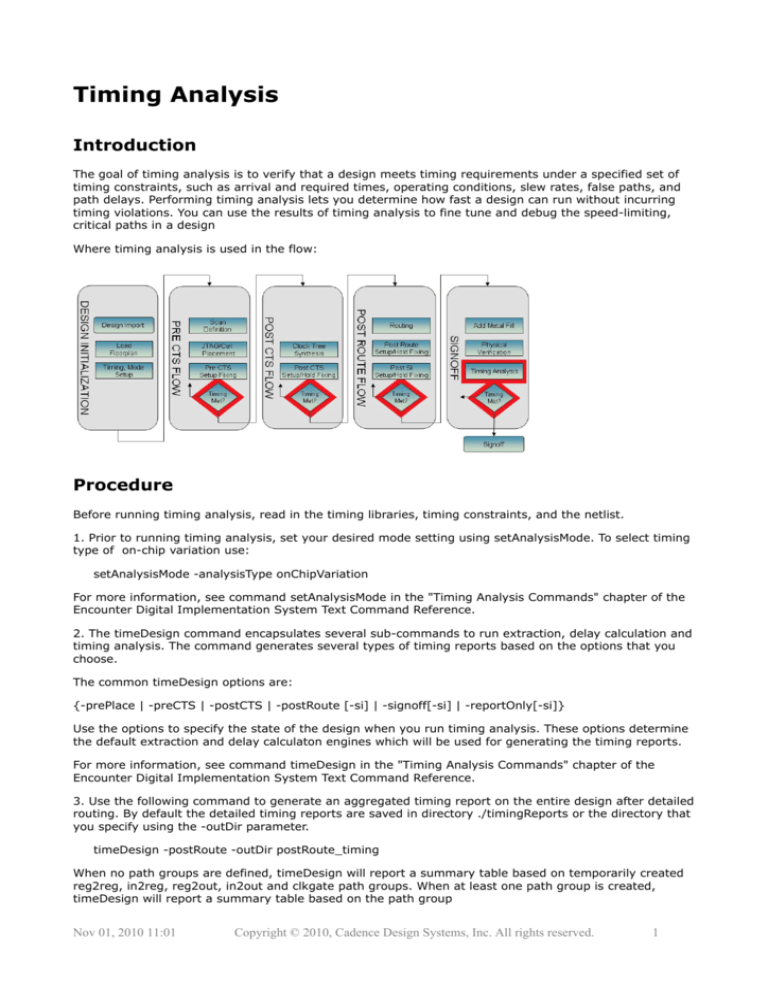

Where timing analysis is used in the flow:

Procedure

Before running timing analysis, read in the timing libraries, timing constraints, and the netlist.

1. Prior to running timing analysis, set your desired mode setting using setAnalysisMode. To select timing

type of on-chip variation use:

setAnalysisMode -analysisType onChipVariation

For more information, see command setAnalysisMode in the "Timing Analysis Commands" chapter of the

Encounter Digital Implementation System Text Command Reference.

2. The timeDesign command encapsulates several sub-commands to run extraction, delay calculation and

timing analysis. The command generates several types of timing reports based on the options that you

choose.

The common timeDesign options are:

{-prePlace | -preCTS | -postCTS | -postRoute [-si] | -signoff[-si] | -reportOnly[-si]}

Use the options to specify the state of the design when you run timing analysis. These options determine

the default extraction and delay calculaton engines which will be used for generating the timing reports.

For more information, see command timeDesign in the "Timing Analysis Commands" chapter of the

Encounter Digital Implementation System Text Command Reference.

3. Use the following command to generate an aggregated timing report on the entire design after detailed

routing. By default the detailed timing reports are saved in directory ./timingReports or the directory that

you specify using the -outDir parameter.

timeDesign -postRoute -outDir postRoute_timing

When no path groups are defined, timeDesign will report a summary table based on temporarily created

reg2reg, in2reg, reg2out, in2out and clkgate path groups. When at least one path group is created,

timeDesign will report a summary table based on the path group

Nov 01, 2010 11:01

Copyright © 2010, Cadence Design Systems, Inc. All rights reserved.

1

By default, timeDesign reports setup timing. To report hold checks, -hold option needs to be used.

timeDesign -hold

For Multi-Mode Multi-Corner (MMMC) designs, timeDesign reports the timing for each active analysis

view, as well as an aggregated summary.

4. Use command report_timing to generate timing reports on specific paths. You can use the -format

option to customize the report fields

Examples

To generate an aggregated timing report summary prior to CTS, use the following command. This

command runs Trial Route, native default extraction, and timing analysis to generate timing reports

before clock tree synthesis:

timeDesign -preCTS

The following example shows an aggregated summary report generated by timeDesign:

The following command ignores the net load and runs timing analysis before the design is placed.

timeDesign -prePlace

The following commands use native detailed extraction and timing analysis to generate timing reports for

both setup and hold after the design has been routed.

timeDesign -postRoute

timeDesign -postRoute -hold

The following command runs timing analysis for signoff taking into account effects of signal integrity and

using QRC engine for extraction:

timeDesign -signoff -si

Nov 01, 2010 11:01

Copyright © 2010, Cadence Design Systems, Inc. All rights reserved.

2

The following command specifies the use of existing extraction and timing analysis data to generate

timing reports. When you use this parameter, the software does not run extraction or timing analysis;

instead it uses data that is already in memory.

timeDesign -reportOnly

To generate a timing report on the most critical path which traces complete launch and capture clock

paths, run the following command:

report_timing -path_type full_clock

You can use the -format parameter to customize which columns displayed when running command

report_timing. Valid format columns are: adjustment, annotation, arc, arrival, cell, delay, direction,

edge, fanin, fanout, incr_delay, instance, instance_location, load, locv_derate, net, phase, pin, hpin,

pin_location, required, retime_delay, retime_slew, slew, stolen, and user_derate.

To display columns: cell, delay, fanout, instance, load, net and slew, run the following command:

report_timing -format {cell delay fanout instance load net slew}

By default, the following columns are displayed when running report_timing:

{instance arc cell delay arrival required}

Alternatively, you can permanently set the desired columns using :

set_global report_timing_format

This will display the specified columns each time report_timing is called. For example:

set_global report_timing_format {cell delay fanout instance load net slew}

report_timing

Nov 01, 2010 11:01

Copyright © 2010, Cadence Design Systems, Inc. All rights reserved.

3